### **FEATURES**

- Control

- Controller and integrated bus interface total solution for IEEE 802.3, 10BASE5, 10BASE2 and 10BASE-T

- Software-compatible with industry standard Ethernet adapters:

- \* Novell®'s NE 2000

- \* Western Digital/SMC's (8003E, 8003EBT, 8013EBT)

- Selectable buffer memory size

- No external bus logic or drivers

- Integrated controller, MCC and transceiver

- Full IEEE 802.3 AUI interface

- Single 5V supply

- Software-compatible with DP8390, DP83901 and DP83902

- Efficient buffer management implementation

- MCC module (Manchester Code Converter, also called ENDEC)

- 10 Mbit/s Manchester encoding/decoding

- Squelch on receive and collision pairs

- TPI module (10BASE-T) transceiver

- Transmitter and receiver functions

- Collision detect, heartbeat and jabber

- Selectable link integrity test or link disable

- Polarity detection/correction

- Provides more powerful functions than NS DP83905

- Supports 15 I/O bases instead of 7

- Direct ID PROM access through I/O port instead of through remote DMA

- Auto configuration function-supported makes jumperless more powerful

- Solution for multiple LAN cards I/O bases conflict problem to make manufacture more efficient.

- Supports "write ID back to EEPROM" function instead of just writing configuration back to EEPROM to make manufacture more efficient.

- Modify current configurations without turning off power

- Variety of EEPROM supported

#### **GENERAL DESCRIPTION**

The MX98905 is designed for easy implementation of CSMA/CD local area networks, which include Ethernet® (10BASE5), Thin Ethernet (10BASE2), and Twisted-pair Ethernet (10BASE-T). The Media Access Control (MAC) and Encode-Decode (ENDEC) are provided with an AUI interface. The 10BASE-T transceiver functions according to the IEEE 802.3 standards, and the MX98905 10BASE-T transceiver operations in compliance with the IEEE standard.

The functional block of the MX98905 consists of the integration of the entire bus interface for PC-AT® (Industry Standard Architecture, ISA) bus-based systems, receiver, transmitter, collision, heartbeat, loopback, jabber, and link integrity blocks. When combined with equalization resistors, the transceiver transmits or receives filters, and pulse transformers provide physical interface from the ENDEC module of the MX98905 and the twisted-pair medium.

When software and hardware are properly configured, the MX98905 can be set to be compatible with either the NE2000 or EtherCard PLUS16<sup>™</sup>. All bus drivers and control logic are integrated inside the chip to reduce LAN card cost and area.

Manchester encoding and decoding is made possible through the integrated ENDEC by means of a differential transceiver and phase lock loop decoder at 10 Mbit/sec. Collision detect translator and diagnostic loopback capability are included in this process. Interfacing directly with the transceiver module, the ENDEC module also provides a fully IEEE-compliant AUI (Attachment Unit Interface) to connect with other media transceivers.

The Media Access Control function, provided by the Ethernet Network Control (ENC) module, effects an efficient packet transmission and reception control through unique dual DMA channels and an internal FIFO. To lessen board cost and area overheads, bus arbitration and memory control logic are integrated.

Designed for easy interface with other transceivers by means of the AUI interface, the MX98905 provides a thorough single chip solution for 10BASE-T IEEE 802.3 network.

Constraints of CMOS processing require that isolation, whether capacitive or inductive, be used at the AUI differential signal interface for 10BASE5 and 10BASE2 applications.

P/N: PM0365 1 REV. 1.3, NOV 20 ,1995

### Note:

TRI-STATE® is a registered trademark of National Semiconductor.

PC-AT® is a register trademark of International Business Machines Corp.

Novell® is a registered trademark of Novell Inc. EtherCard PLUS™ and EtherCard PLUS 16™ are trademarks of standard Microsystems Corp.

Ethernet® is a registered trademark of Xerox Corp.

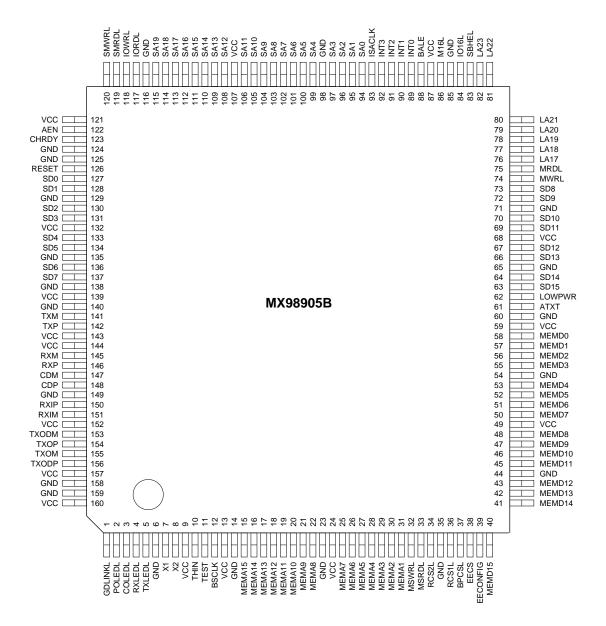

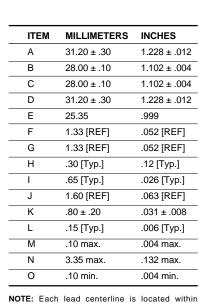

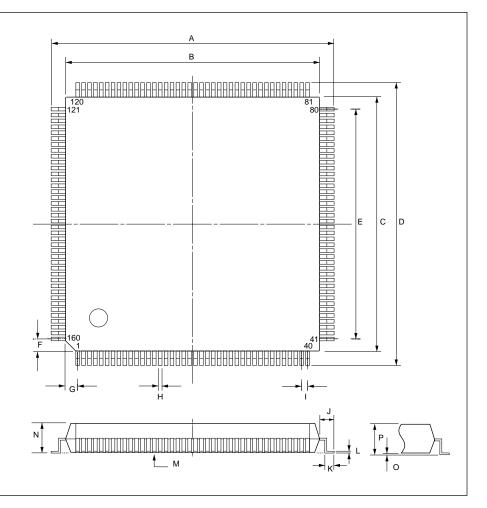

### PIN CONFIGURATION

# **PIN DESCRIPTIONS**

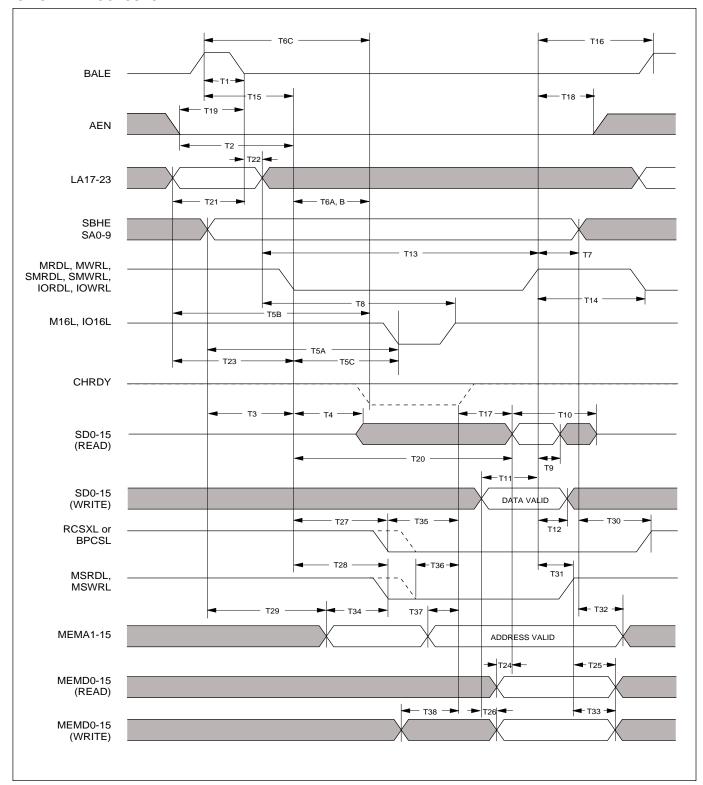

# A. ISA BUS INTERFACE

| SYMBOL    | PIN TYPE | PIN NUMBER                                                                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                |  |

|-----------|----------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SA0-SA19  | I        | 94-97, 99-106,<br>108-115                                                         | LATCHED ADDRESS BUS: Low-order bits of the system's 24-address bus. These lines are enabled onto the bus when BALE high and latched when BALE is deasserted. The MX98905 us these bits to decode the boot PROM address and internal registe In shared memory mode, they are used to decode accesses memory of the MX98905. |  |

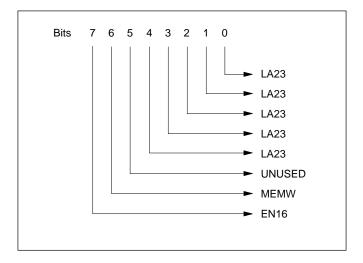

| LA17-LA23 | I        | 76-82                                                                             | UNLATCHED ADDRESS BUS: High-order 7 bits of the 24-bit system address bus. These lines are valid on the falling edge of BALE. The MX98905 uses these bits to decode shared memory address is shared memory mode. The validity of M16L depends on these signals only.                                                       |  |

| SD0-SD15  | I/O      | 127, 128, 130,<br>131, 133, 134,<br>136, 137, 73, 72<br>70, 69, 67,<br>66, 64, 63 | SYSTEM DATA BUS: 16-bit system data bus. Used to transfer data between the system and the MX98905.                                                                                                                                                                                                                         |  |

| BALE      | I        | 88                                                                                | BUS ADDRESS LATCH ENABLE: Active-high signal. Used to late valid addresses from the current Bus Master on the falling edge BALE.                                                                                                                                                                                           |  |

| SBHEL     | 1        | 83                                                                                | SYSTEM BUS HIGH ENABLE: Active-low. Indicates that the system expects a transfer on the address on the bus is 16 bits wide.                                                                                                                                                                                                |  |

| IO16L     | 0        | 84                                                                                | 16-BIT I/O TRANSFER: Active-low. In I/O mode this signal indicates that the MX98905 is responding to a 16-bit I/O access by driving 16 bits of data on SD0-SD15.                                                                                                                                                           |  |

| M16L      | 0        | 86                                                                                | 16-BIT MEMORY TRANSFER: Active-low.                                                                                                                                                                                                                                                                                        |  |

| MWRL      | 1        | 74                                                                                | MEMORY WRITE STROBE: Active-low. System uses this signal to write to the memory map of the MX98905.                                                                                                                                                                                                                        |  |

| MRDL      | 1        | 75                                                                                | MEMORY READ STROBE: Active-low. System uses this signal to read from the memory map of the MX98905.                                                                                                                                                                                                                        |  |

| SMR/IRL,  | I        | 119, 120                                                                          | LOW MEMORY STROBES: Active-low. The MX98905 uses MRDL and MWRL in 16-bit memory mode and will use SMRDL and SMRL in memory mode when ATXT is low (8-bit mode). Note that SMRDL and SMWRL are also used to access the BOOT PROM.                                                                                            |  |

| IOWRL     | I        | 118                                                                               | I/O WRITE STROBE: Active-low. Strobe from system to write to the I/O Map of the MX98905.                                                                                                                                                                                                                                   |  |

| IORDL     | I        | 117                                                                               | I/O READ STROBE: Active-low. Strobe from system to read from the I/O Map of the MX98905.                                                                                                                                                                                                                                   |  |

# A. ISA BUS INTERFACE (Continued)

| SYMBOL    | PIN TYPE | PIN NUMBER | DESCRIPTION                                                                                                                                                                                                                                |  |

|-----------|----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RESET     | I        | 126        | RESET: Active high. Used to reset all devices on the bus. T MX98905 will recognize this signal only when the duration of the signal is larger than 400 ns.                                                                                 |  |

| CHRDY     | 0        | 123        | CHANNEL READY: Used to insert wait states into system accesses                                                                                                                                                                             |  |

| AEN       | I        | 122        | DMA ACTIVE: Indicates that the address lines are driven by a DN controller.                                                                                                                                                                |  |

| INTO-INT3 | 0        | 89-92      | INTERRUPT REQUEST: Activation or not of these 4 signals is determined by Configuration Registers A and C. They can be use to either directly drive the interrupt lines or used as a 3-bit code with strobe to generate up to 8 interrupts. |  |

| ATXT      | 1        | 61         | 8/16 BIT SLOT SELECT: Indicates that the MX98905 is in 8- or 16 bit ISA bus. It is in 16-bit mode when ATXT is high ATXT has internated pulldown register; if left unconnected, 8-bit mode is the default mode.                            |  |

| ISACLK    | I        | 93         | ISA CLOCK: Clock from ISA bus.                                                                                                                                                                                                             |  |

# **B. NETWORK INTERFACE**

| SYMBOL                            | PIN TYPE | PIN NUMBER | DESCRIPTION                                                                                                                                                                                                                                             |  |

|-----------------------------------|----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| POLEDL                            | 0        | 2          | POLARITY LED: Active-low signal. When the MX98905 detects seven consecutive link pulses or three consecutive received packets with reversed polarity, POLEDL is asserted.                                                                               |  |

| TXLEDL                            | 0        | 5          | TRANSMIT LED: Active-low signal. It is asserted for approximately 50ms whenever the MX98905 transmits data in either AUI or TPI modes.                                                                                                                  |  |

| RXLEDL                            | 0        | 4          | RECEIVE LED: Active-low signal. An open-drain output. It is asserted for approximately 50ms whenever valid received data is detected while in AUI or TPI modes.                                                                                         |  |

| COLEDL                            | 0        | 3          | COLLISION LED: An open-drain active-low signal. It is asserted for approximately 50ms whenever collision is detected while in AUI or TPI modes.                                                                                                         |  |

| GDLINKL                           | 0        | 1          | GOOD LINK LED: An open-drain active-low signal. Used to display link integrity status.                                                                                                                                                                  |  |

|                                   |          |            | OFF (when high): A. MX98905 is in AUI mode B. MX9805E is in TPI mode, link testing is enabled and link integrity is bad.                                                                                                                                |  |

|                                   |          |            | ON (when low): A. Link testing is disabled B. Link testing is enabled and link integrity is good.                                                                                                                                                       |  |

| X1                                | I        | 7          | Crystal or external oscillator input.                                                                                                                                                                                                                   |  |

| X2                                | 0        | 8          | CRYSTEL FEEDBACK OUTPUT: Used in crystal connection only. Should be left completely unconnected when using an oscillator module.                                                                                                                        |  |

| THIN                              | 0        | 10         | THIN CABLE: Active-high signal. It is high when the MX98905 is configured for thin cable (program PHY1 and PHY0 of Configuration B). This signal can be used to turn on the DC-DC converter required by thin Ethernet.                                  |  |

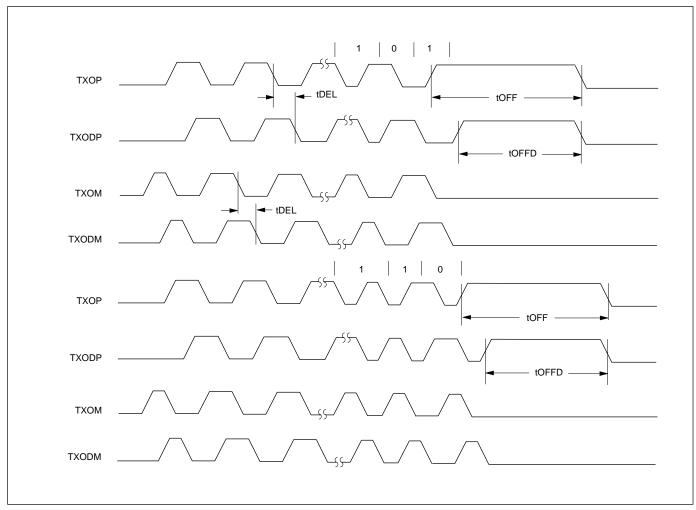

| TXODP,<br>TXOM,<br>TXOP,<br>TXODM | 0        | 156-153    | TWISTED-PAIR TRANSMIT OUTPUTS: These high-drive CMOS level outputs are resistively combined external to the chip to produce a differential output signal with equalization to compensate for intersymbol interference (ISI) on the twisted-pair medium. |  |

# B. NETWORK INTERFACE (Continued)

| SYMBOL     | PIN TYPE | PIN NUMBER | DESCRIPTION                                                                                                                                                    |  |  |

|------------|----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

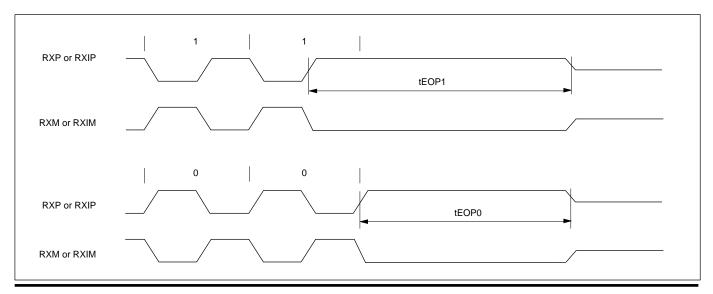

| RXIP, RXIM | I        | 150-151    | TWISTED-PAIR RECEIVE INPUTS: These inputs feed a differential amplifier which passes valid data to the MCC module.                                             |  |  |

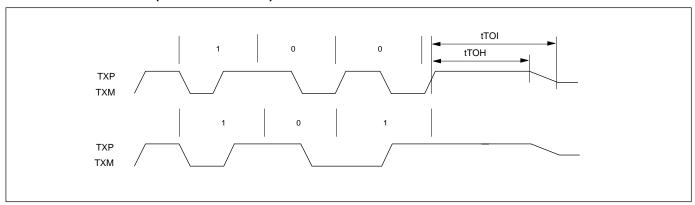

| TXM, TXP   | 0        | 141-142    | AUI TRANSMIT OUTPUT: Differential driver which sends t encoded data to the transceiver. The outputs are source follow which requires 270 w pulldown resistors. |  |  |

| RXM, RXP   | 1        | 145-146    | AUI RECEIVE INPUTS: Differential receive input pair from the transceiver.                                                                                      |  |  |

| CDM, CDP   | I        | 147-148    | AUI COLLISION INPUTS: Differential collision pair input from the transceiver cable.                                                                            |  |  |

# C. EXTERNAL MEMORY SUPPORT

| SYMBOL                         | PIN TYPE | PIN NUMBER | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|--------------------------------|----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

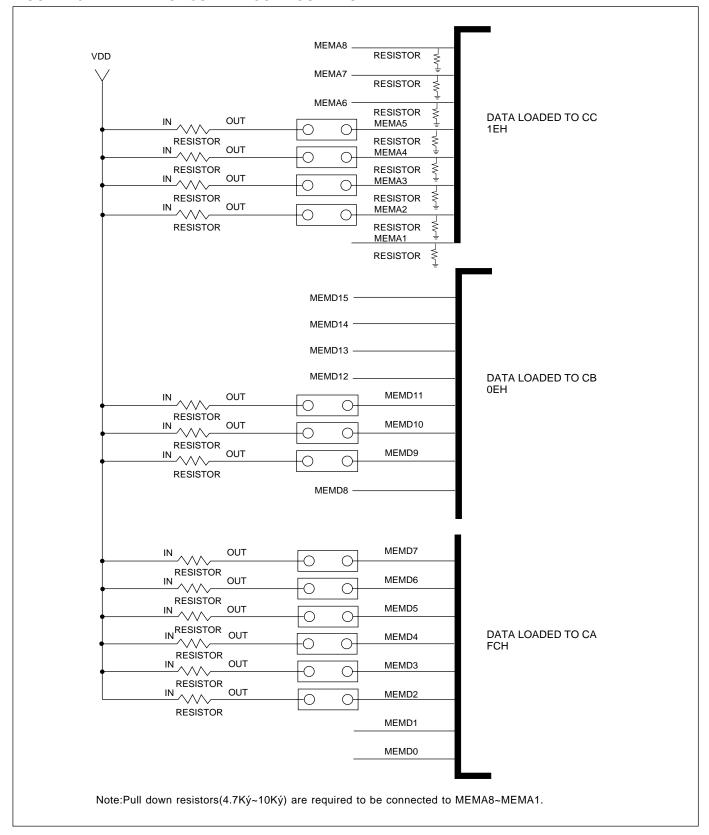

| MEMD0-7<br>CA0-7<br>DO, DI, SK | I/O      | 58-55      | MEMORY SUPPORT DATA BUS; CONFIGURATION REGISTER A INPUT; EEPROM SIGNALS.  MEMD0-7: These pins can be used to access external memory (RAM) and boot PROM while RESET is inactive.  CA0-7: When RESET is active more than 400 ms, Configuration Register A is loaded with the value on these pins on the falling edge of RESET signal. These 8 bits have internal pulldown resistors, hence if the pin is left unconnected the corresponding register bit is 0.  DO, DI, SK: When RESET goes from an active to an inactive level the MX98905 will read the contents of an EEPROM. At this moment DO = MEMD0, DI = MEMD1 and SK = MEMD2. The value read from EEPROM will be stored in Configuration Registers and PROM space |  |

| MEMD8-15                       | I/O      | 48-45      | MEMORY SUPPORT DATA BUS; CONFIGURATION REGISTER INPUT.  MEMD8-15: These pins can be used to access external memo when RESET is inactive.  CB0-7: When RESET is active more than 400 ms, Configuration Register B is loaded with the value on these pins on the falling edge of RESET signal. These 8 bits have internal pulldown register hence if the pin is left unconnected the corresponding register bit 0.                                                                                                                                                                                                                                                                                                          |  |

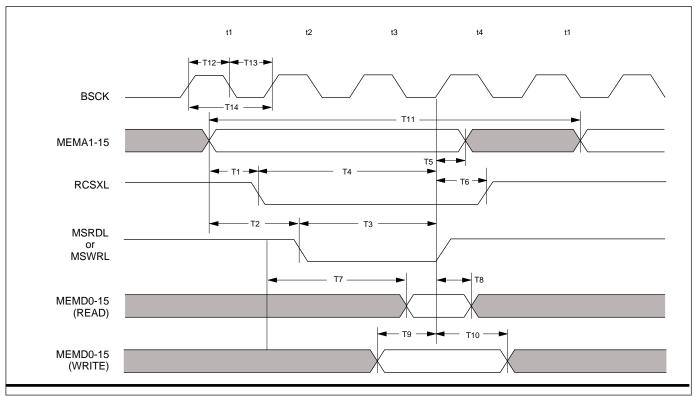

| MEMA1-8                        | I/O      | 31-25, 22  | MEMORY SUPPORT ADDRESS BUS; CONFIGURATION REGITER C INPUT.  MEMA1-8: These pins can be used to drive external memoral address bus when RESET is inactive.  CC0-7: When RESET is active more than 400 ms, Configuration Register C is loaded with the value on these pins on the falling edge of RESET signal. For application without EEPROM (i.e. EECONF is low) and try to load configuration data to CC from these eight pinexternal resistor is necessary.                                                                                                                                                                                                                                                            |  |

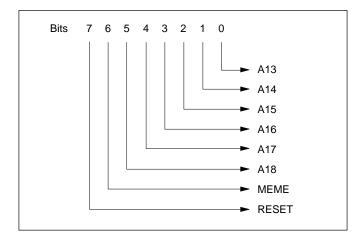

| MEMA9-15                       | 0        | 21-15      | MEMORY SUPPORT ADDRESS: These pins can be used to drive external memory address bus when RESET is inactive. When the memory is only 8 bits wide (single RAM) and the MX98905 is in compatible mode, A0 will appear on A13; and on A15 in non compatible mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| MSRDL                          | 0        | 33         | MEMORY SUPPORT BUS READ: Strobes data from the external RAM into the MX98905 through the memory support data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| MSWRL                          | 0        | 32         | MEMORY SUPPORT BUS WRITE: Strobes data from the MX98905 into the external RAM via the memory support data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| BPCSL                          | 0        | 37         | BOOT PROM CHIP SELECT: Active-low signal for selecting the Boot PROM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

# C. EXTERNAL MEMORY SUPPORT (Continued)

| SYMBOL   | PIN TYPE | PIN NUMBER | DESCRIPTION                                                                                                                                                   |  |

|----------|----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RCS1L    | 0        | 36         | RAM CHIP SELECT 1: Active-low signal to drive the CS signal of t external RAM on the lower half of the memory-supported data bu                               |  |

| RCS2L    | 0        | 34         | RAM CHIP SELECT 2: Active-low signal to drive the CS signal external RAM on the upper half of the memory-supported data but                                   |  |

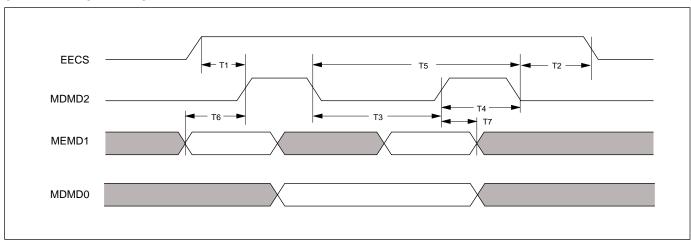

| EECS     | 0        | 38         | EEPROM CHIP SELECT: Active-high signal to drive the CS signal the external EEPROM.                                                                            |  |

| EECONFIG | 1        | 39         | CONFIGURE FROM EEPROM: The MX98905 will NOT load confirations from EEPROM if this pin is low during power-on reset.                                           |  |

| BSCLK    | I        | 12         | INTERNAL BUS CLOCK: This pin controls the speed of the controller DMA function. When CLKSEL of configuration C is set low, this pin should be tied to ground. |  |

# D. LOW POWER SUPPORT

| SYMBOL | PIN TYPE | PIN NUMBER | DESCRIPTION                                                                                                                |

|--------|----------|------------|----------------------------------------------------------------------------------------------------------------------------|

| LOWPWR | I        | 62         | LOW POWER: When it is high, the MX98905 enters its low-power mode. This pin should be tied to ground for normal operation. |

# **E. TEST SUPPORT**

| _ | SYMBOL | PIN TYPE | PIN NUMBER | DESCRIPTION                                                                                                                                   |

|---|--------|----------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| _ | TEST   | I        | 11         | TEST: This pin is only used for industry test. It should be left unconnected in normal operation (because it has internal pulldown resistor). |

# F. POWER SUPPLY PINS

| SYMBOL | PIN TYPE | PIN NUMBER                                                                                                 | DESCRIPTION          |

|--------|----------|------------------------------------------------------------------------------------------------------------|----------------------|

| VCC    | I        | 160, 157, 152,<br>144, 143, 9, 59,<br>49, 24, 13, 132,<br>121, 107, 87, 68,13                              | 5V POWER SUPPLY PIN. |

| GND    | I        | 159, 158, 149,<br>140, 138, 6, 60,<br>54, 44, 35, 23, 14,<br>135, 129, 125,<br>124, 116, 98, 85,<br>71, 65 | GND SUPPLY PIN.      |

## **FUNCTIONAL DESCRIPTION**

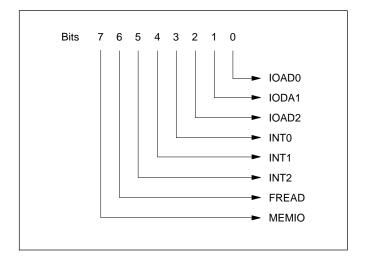

## 1. I/O BASES DETERMINATION

The I/O bases are determined by 6 bits in the MX98905. They are: IOAD2-0 in Configuration A (CA); PAGE and IOBEN in Hidden Configuration Register (HCFR) and HCFRE in Hidden Command Register (HCMR). For details about HCMR and HCFR (Registers provided by

the MX98905 only) see Register Description. User can directly modify the value of PAGE and IOAD2-0 to change I/O base or use AUTO configuration feature provided by the MX98905. See Enhanced mode description for details about AUTO configuration.

The following are the I/O bases mapping:

TABLE 1. I/O BASES MAPPING

| HCMR  | HCFR  | HCFR |       | CA    |       |               |

|-------|-------|------|-------|-------|-------|---------------|

| HCFRE | IOBEN | PAGE | IOAD2 | IOAD1 | IOAD0 | I/O BASE      |

| 0     | Х     | Х    | 0     | 0     | 0     | 300H          |

| 1     | Χ     | Χ    | 0     | 0     | 1     | Not supported |

| 0     | Χ     | Χ    | 0     | 1     | 0     | 240H          |

| 0     | Χ     | Χ    | 0     | 1     | 1     | 280H          |

| 0     | Χ     | X    | 1     | 0     | 0     | 2C0H          |

| 0     | Χ     | X    | 1     | 0     | 1     | 320H          |

| 0     | Χ     | X    | 1     | 1     | 0     | 340H          |

| 0     | Χ     | Χ    | 1     | 1     | 1     | 360H          |

| 1     | 0     | Х    | 0     | 0     | 0     | 300H          |

| 1     | 0     | X    | 0     | 0     | 1     | Not supported |

| 1     | 0     | X    | 0     | 1     | 0     | 240H          |

| 1     | 0     | X    | 0     | 1     | 1     | 280H          |

| 1     | 0     | X    | 1     | 0     | 0     | 2C0H          |

| 1     | 0     | Χ    | 1     | 0     | 1     | 320H          |

| 1     | 0     | Χ    | 1     | 1     | 0     | 340H          |

| 1     | 0     | Χ    | 1     | 1     | 1     | 360H          |

| 1     | 1     | 0    | 0     | 0     | 0     | 300H          |

| 1     | 1     | 0    | 0     | 0     | 1     | Not supported |

| 1     | 1     | 0    | 0     | 1     | 0     | 240H          |

| 1     | 1     | 0    | 0     | 1     | 1     | 280H          |

| 1     | 1     | 0    | 1     | 0     | 0     | 2C0H          |

| 1     | 1     | 0    | 1     | 0     | 1     | 320H          |

| 1     | 1     | 0    | 1     | 1     | 0     | 340H          |

| 1     | 1     | 0    | 1     | 1     | 1     | 360H          |

P/N: PM0365 REV. 1.3, NOV 20 ,1995

| HCMR  | HCFR  |      |       | CA    |       |          |  |

|-------|-------|------|-------|-------|-------|----------|--|

| HCFRE | IOBEN | PAGE | IOAD2 | IOAD1 | IOAD0 | I/O BASE |  |

| 1     | 1     | 1    | 0     | 0     | 0     | 380H     |  |

| 1     | 1     | 1    | 0     | 0     | 1     | 3A0H     |  |

| 1     | 1     | 1    | 0     | 1     | 0     | 3C0H     |  |

| 1     | 1     | 1    | 0     | 1     | 1     | 3E0H     |  |

| 1     | 1     | 1    | 1     | 0     | 0     | 200H     |  |

| 1     | 1     | 1    | 1     | 0     | 1     | 220H     |  |

| 1     | 1     | 1    | 1     | 1     | 0     | 2A0H     |  |

| 1     | 1     | 1    | 1     | 1     | 1     | 2E0H     |  |

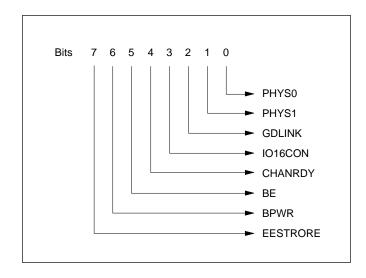

HCFRE, IOBEN and PAGE are powered on low if software driver doesn't alter the value of these bits. The I/O bases of the MX98905 are fully compatible with DP83905.

### 2. SHARED MEMORY COMPATIBLE MODE

This mode is compatible with the EtherCARD PLUS16. I/ O address mapping and Memory mapping will be described subsequently.

After I/O Base is determined, the following structure appears:

## 2.1 I/O Address Mapping

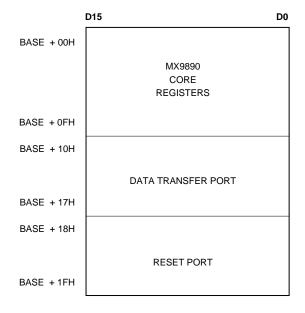

#### FIGURE 2. SHARED MEMORY MODE REGISTER MAPPING

|            | IORDL     | IOWRL    |  |  |  |  |

|------------|-----------|----------|--|--|--|--|

| BASE + 00H |           |          |  |  |  |  |

| BASE + 01H | AT DETECT | CONTROL1 |  |  |  |  |

|            |           |          |  |  |  |  |

| BASE + 05H |           | CONTROL2 |  |  |  |  |

|            |           |          |  |  |  |  |

| BASE + 08H |           |          |  |  |  |  |

|            | PROM      |          |  |  |  |  |

| BASE + 0FH |           |          |  |  |  |  |

| BASE + 10H |           |          |  |  |  |  |

|            | MX9890    |          |  |  |  |  |

|            | CORE      |          |  |  |  |  |

| BASE + 1FH | REGISTERS |          |  |  |  |  |

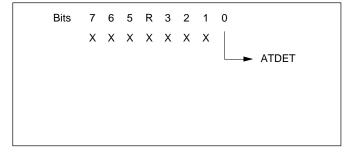

The AT Detect register indicates whether the MX98905 is in an 8- or 16-bit slot. The MX98905 uses the falling edge of RESET to latch the value shown on ATXT to determine the value of ATDET.

Address 08H to 0FH are specified as PROM space. The contents of PROM are loaded from EEPROM during power-on reset. User should program the EEPROM to contain these value. In enhanced mode of the MX98905, the contents of PROM can be written back to EEPROM. See enhanced mode description for details.

# 2.2 Memory Address Mapping

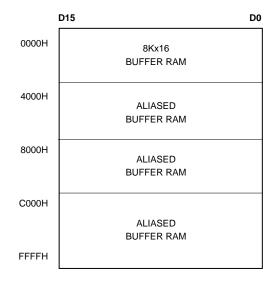

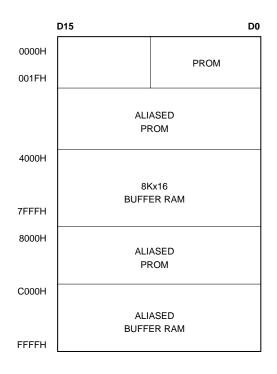

FIGURE3. SHARED MEMORY MODE ENC CORE MEMORY MAP

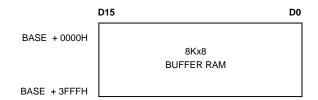

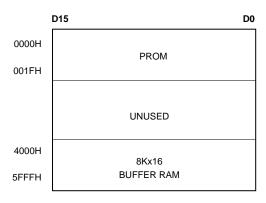

### FIGURE 4. SHARED MEMORY MODE HOST MEMORY MAP FOR 8 KBYTES BUFFER RAM

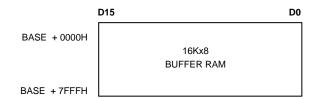

## FIGURE 5. SHARED MEMORY MODE HOST MEMORY MAP FOR 16 KBYTES BUFFER RAM

The 8 kwords of memory can be accessed directly by the host system in the same manner as any other memory. Typically the programmer can remove data from this buffer using a "MOV" or "MOVSW" instruction.

In compatible mode, data located at address 4000h-7FFFH, 8000H-BFFFH and C000H-FFFFH is just the mirror of contents located at 0000H-3FFFH.

2.3 Configuration vs. Operation

| Byte Byte |

|-----------|

| ·         |

| Byte      |

| = j · •   |

| Byte/Word |

| Byte      |

| Byte      |

| Byte      |

| Byte/Word |

| _         |

# 2.4 SRAM Size vs. MEMA[15:1]

| SRAMSIZE | MEMA15 | MEMA14 | MEMA13 | RCS1L    | RCS2L |

|----------|--------|--------|--------|----------|-------|

| 8K       | 0      | 1      | A0     | Even/Odd | X     |

| 16K      | 0      | 1      | A13    | Even     | Odd   |

| 32K      | A0     | A14    | A13    | Even/Odd | Х     |

| 64K      | A15    | A14    | A13    | Even     | Odd   |

### 3. SHARED MEMORY NON-COMPATIBLE MODE

The difference between compatible and non-compatible mode is that the non-compatible mode maps a full 64 kbytes of RAM into the PC's memory address space instead of 8 kbytes. The I/O map for both modes is the same.

#### 4. 16-BIT I/O PORT COMPATIBLE MODE

This mode is compatible with the Novel NE2000. I/O address mapping and Memory mapping will be shown in the following subsection.

After I/O base is determined, the following structure appears:

## 4.1 I/O Address Mapping

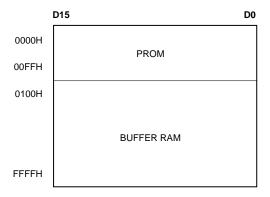

#### FIGURE 6. I/O MODE I/O PORT MAP

The registers within this area are 8 bits wide, but the data transfer port is 16 bits wide. By programming the ENC's internal registers, the user can issue Remote DMA to transfer data between the data port and the external memory.

# 4.2 Memory Address Mapping

#### FIGURE 7. I/O MODE MEMORY MAP

The MX98905 Controller has a 64K address range, but only does partial decoding on these devices. The PROM data is mirrored at all decodes up to 4000H and the entire map is repeated at 8000H. In order to access either the PROM or the RAM, the user must initiate a Remote DMA transfer between the I/O port (see I/O map) and the memory.

Address 00H to 1FH are specified as the PROM space to make the MX98905 compatible with NE2000. Similar to shared memory map, this is actually an array of 8-bit registers which are loaded from EEPROM during power-on reset. User should prepare data in the EEPROM as show in the format.

For user's convenience, the MX98905 provides an enhanced mode to facilitate software to access the contents of ID PROM -- Read ID PROM through I/O port. User can refer to Enhanced mode description for details.

## 4.3 PROM Map

TABLE 2.

| LOCATION CONTENTS         |

|---------------------------|

| EtherNet Address 0 (MSB)  |

| EtherNet Address 1        |

| EtherNet Address 2        |

| EtherNet Address 3        |

| EtherNet Address 4        |

| EtherNet Address 5        |

| 00H                       |

| 57H                       |

| EtherNet Address 0 thru 5 |

| Reserved                  |

| 42H                       |

|                           |

The upper two addresses of the PROM store contain bytes that identify whether the MX98905 Controller is in 8- or 16-bit mode. For 16-bit mode the values of these bytes are 57H; for 8-bit mode they both contain 42H. Software driver can read these two bytes to determine whether the Controller is in 8- or 16-bit mode.

#### 5. 8-BIT I/O PORT COMPATIBLE MODE

In 8-bit I/O port compatible mode, the I/O mapping is the same as in 16-bit mode. The memory map for 8-bit I/O port compatible mode is shown below:

FIGURE 8. I/O MODE 8-BIT MEMORY MAP

### 6. I/O PORT NON-COMPATIBLE MODE

Although this mode is similar to Novell's NE2000, it also allows the user to use the full 64 kbytes of address space except for an initial page for the PROM. I/O map is the same as compatible mode. Memory map is shown below:

FIGURE 9. I/O MODE NON-COMPATIBLE MODE MEMORY MAP

Although the PROM occupies 256 bytes, it is only 16 bytes long. There is a partial decode inside the MX98905 so the PROM is mirrored at 16 addresses in this region.

## 7. POWER-ON RESET OPERATION

When the duration of RESET signal is longer than 400ns, the MX98905 will read configurations from EEPROM depending on the value shown on EECONFIG pin. User should prepare all the data the MX98905 needs in the EEPROM before switching on the PC. The following table shows the format of EEPROM:

### **TABLE 3. EEPROM DATA MAPPING**

| D15         | D0                 |

|-------------|--------------------|

| NOT USED    | CONFIG. C          |

| CONFIG. B   | CONFIG. A          |

| •           | •                  |

| •           | •                  |

| •           | •                  |

| 42H         | 42H                |

| 57H         | 57H                |

| •           | •                  |

| •           | •                  |

| •           | •                  |

| RESERVED    | RESERVED           |

| (CHECKSUM)  | (BOARD TYPE)       |

| ETEHR ADD 5 | ETHER ADD 4        |

| ETHER ADD 3 | ETEHR ADD 2        |

| ETEHR ADD 1 | ETEHR ADD 0        |

|             | NOT USED CONFIG. B |

values shown on parentheses are for Shared memory map only. For the shared memory mode, the two's complement of these eight bytes (00-03H) should be equal to FFH.

High byte of 0FH is not used in NS DP83905 compatible mode, but the value will be loaded into Hidden ConFiguration Register (HCFR) inside the MX98905 in enhanced mode. See Enhanced mode description for details.

## 7.1 Valid Power-On Reset

The MX98905 is equipped with a filter to screen out RESET signal whenever its duration is less than 400ns. The default value of each Configuration Register is:

Configuration Register A: 39H Configuration Register B: 00H Configuration Register C: 00H

When RESET is active more than 400ns, the MX98905 will recognize such action and begin its power-on reset algorithm. At this moment, all I/O will be disabled

except the RESET signal. On the falling edge of RESET signal, the MX98905 will load data shown on MEMD0-7, MEMD8-15 and MEMA1-8 into Configuration Register A, B and C, respectively. The value loaded from jumper will overwrite the default value.

Figure 10 shows the example for jumper configuration.

After loading jumper value into relative Configuration Registers, the MX98905 will execute EEPROM operation, which depends on the value of EECONFIG. If EECONFIG is high, then both the configuration and ID PROM data will be loaded into the MX98905; otherwise, only ID PROM data is loaded.

## 7.2 EEPROM Operation

During EEPROM operation, all internal registers are inaccessible. If EECONFIG is high, then the configurations loaded from EEPROM will overwrite the value loaded from jumper selection. Configurations loaded from EEPROM will be stored in Configuration Registers and Ether ID will be stored in PROM space inside the MX98905 (refer to PROM MAP for details).

### 7.2.1 Load Configurations from EEPROM

When EECONFIG is set to high, configurations stored in EPPROM will be loaded into MX98905. After loading configurations fom EEPROM, following sequence depends on the value of ATXT:

ATXT= 1:00H-07H ATXT= 0:00H-06H, 08H

EECONFIG = 1 : OEH (Configuration A, B), OFH

DWID = 1 (Configuration C),00H - 02H (Ether

Address 0 theu 5) and 03H - 07H

EECONFIG = 1 : OEH (Configuration A, B), OFH

DWID = 0 (Configuration C),00H - 02H (Ether

Address 0 true 5)and 03H - 06H and

08H (data 42H)

7.2.2 Without loading configurations from EEPROM

When EECONFIG is set to low, configrations stored in EEPROM will NOT be loaded into the MX98905 depends on

the value of ATXT: ATXT = 1 : 00H-07H ATXT = 0 : 00H-06H,08H

### 8. STORING CONFIGURATION BACK TO EEPROM

To write configuration into the EEPROM, user must follow the procedure specified below:

```

EEPROM_STORE() {

Disable_All_Interrupts();

value = READ (CB);

value = value & GDLINK ;

value = value f EESTORE;

write (CB, value);

// Issue EESTORE

// EESTORE algorithm starts

Read (CB);

write (CB, value_for_CA) ;

// write new

/ /into CA

through CB

write (CB, value_for_CB); // write CB

write (CB, value_for_CC) ; / / write new value

into CC through CB

while (value & EESTORE) {

value = Read(CB);

wait();

Enable_All_Interrupts();

```

FIGURE 10. EXAMPLE OF JUMPER CONFIGURATION

After EEPROM\_STORE is executed, the current configuration will NOT be changed. If user wants to use the new configuration, he should turn the power off and then turn it on to load new configuration into the MX98905 through valid power-on reset.

For user's convenience, the MX98905 provides the feature for software programmer to update the current configuration after EEPROM\_STORE is executed, i.e., you don't have to switch the power to update the configuration. See Enhanced Description for details.

# 9. ENHANCED FEATURE FUNCTIONAL DESCRIPTION

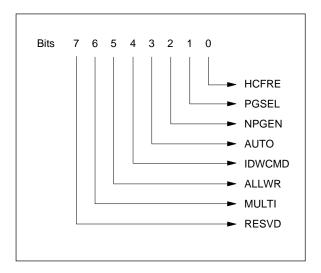

There are two registers, HCMR and HCFR which control the main fuctions of MX98905's enhaned mode. HCMR is the abbreviation of Hidden Command Register and HCFR for Hidden Configuration Register. Bit assignment and function of each bit of HCMR and HCFR will be fully descibed in REGISTER DESCRIPTIONS. For your quick reference, bit assignments of HCMR and HCFR are shown below before we present the enhanced features of MX98905. The following shows the bit assignment for HCMR:

| RESVDMUL | _TI ALLWR | IDECMD | AUTO | NPGEN | PGSEL | HCFRE |

|----------|-----------|--------|------|-------|-------|-------|

|----------|-----------|--------|------|-------|-------|-------|

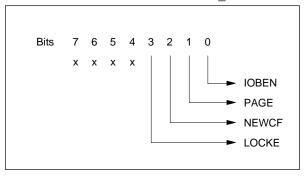

Following shows the bit assignment for HCFR

| RESVD RESVD RESVD RES | VD LOCKE NEWCF | PAGE IOBEN |

|-----------------------|----------------|------------|

|-----------------------|----------------|------------|

## 9.1 Load HCFR From EEPROM

The high-byte value of address 0FH of EEPROM will be loaded into Hidden ConFiguration Register (HCFR) if a valid power-on reset is detected by the MX98905. HCFR is only active when HCFRE bit of HCMR (Hidden CoMmand Register, supported by the MX98905) is set high. If software doesn't alter the value of HCFRE, the value in HCFR has no effect. In the same way, when EEPROM\_STORE algorithm is executed, contents of HCFR will be stored back to EEPROM at the location from where they come.

# 9.2 16 Bytes IDPROM write back function

To write configuration into the EEPROM in either

MX98905 or MX98905A, user must follow the procedure described in section 8.

In MX98905, a "1" value in ALLWR bit will cause the controller to write CA, CB, CC and ID to EEPROM. While in MX98905A, a "1" value in ALLWR bit will write CA, CB, CC, ID, and the rest of 8 bytes from IDPROM registers. i.e. the entire 16 bytes of IDPROM registers can be written back to EEPROM. The other EEPROM write back command is IDWCMD command whose function remains the same as old version.

When loading data from EEPROM during power-on reset, values in IDPROM register byte 15th and 16th are never written back to EEPROM but initialized to correct value according to slot's data width during power-on reset. these two bytes can be modified through software programming.

# 9.3 Update Current Configuration After EEPROM\_STORE is Finished

When NEWCF bit of HCFR is set, the contents of CA, CB and CC will be updated to the value in EEPROM\_STORE algorithm after EEPROM\_STORE algorithm is finished. USER DOESN'T HAVE TO SWITCH THE POWER TO USE THE NEW CONFIGURATION.

# 9.4 Access ID PROM Through I/O Port IN NE2000 Compatible

When NPGEN is high and PGSEL is low (both in HCMR), the MX98905 is programmed to New Page 0. Contents of ID PROM can be directly accessed through I/O port. Table 4 and Table 5 show the address mapping.

## 9.5 Auto Configuration

The MX98905 provides a powerful feature for programmer to program the LAN card in order to avoid the "IO base is conflict with other add\_ on cards" program. When bit 3 (AUTO) of HCMR is set to 1, the MX98905 will change the internal IO base automatically. When software writes to AUTO the first time, the IO base will change to 300H no matter the current IO base is. Susbsequent writing to AUTO bit will make the MX98905 jump to the "next" IO base as described in next paragraph. After AUTO is issued, user can use the information provided below to read the AutoStatus

Register (ASR) to determine whether the IO base is conflict with other add\_ on card(s) or not. When 15 IO base is not enabled (see HCMR register description for more detail), internal state machine will only support 7 IO bases when AUTO is written; if IOBEN of HCFR is set to high (see HCFR register description for more detail), the internal state machine will alter the value of PAGE of HCFR automatically when further IO base is necessary during auto configuration.

The following I/O bases are supported by MX98905. (\*) represents that the IO bases are not supported by MX98905 when 15 IO base is not enabled. 200H (\*), 220H (\*), 240H, 280H,2A0H (\*), 2C0H, 2E0H (\*), 300H, 320H, 340H, 360H, 380H (\*), 3A0H (\*), 3C0H (\*), and 3E0H (\*)

The following IO base and its relative ASR value (shown in parenthses) will be followed after software write an "1" to AUTO bit of HCMR.

TABLE 4. NEW PAGE 0 ADDERSS ASSIGNMENT FOR I/O MAP

| SA003 | READ                 | WRITE                |

|-------|----------------------|----------------------|

| 00H   | PROM BYTE #0 (PB0)   | PROM BYTE #0 (PB0)   |

| 01H   | PROM BYTE #1 (PB1)   | PROM BYTE #1 (PB1)   |

| 02H   | PROM BYTE #2 (PB2)   | PROM BYTE #2 (PB2)   |

| 03H   | PROM BYTE #3 (PB3)   | PROM BYTE #3 (PB3)   |

| 04H   | PROM BYTE #4 (PB4)   | PROM BYTE #4 (PB4)   |

| 05H   | PROM BYTE #5 (PB5)   | PROM BYTE #5 (PB5)   |

| 06H   | PROM BYTE #6 (PB6)   | PROM BYTE #6 (PB6)   |

| 07H   | PROM BYTE #7 (PB7)   | PROM BYTE #7 (PB7)   |

| 08H   | PROM BYTE #8 (PB8)   | PROM BYTE #8 (PB8)   |

| 09H   | PROM BYTE #9 (PB9)   | PROM BYTE #9 (PB9)   |

| 0AH   | PROM BYTE #10 (PB10) | PROM BYTE #10 (PB10) |

| 0BH   | PROM BYTE #11 (PB11) | PROM BYTE #11 (PB11) |

| 0CH   | PROM BYTE #12 (PB12) | PROM BYTE #12 (PB12) |

| 0DH   | PROM BYTE #13 (PB13) | PROM BYTE #13 (PB13) |

| 0EH   | PROM BYTE #14 (PB14) | PROM BYTE #14 (PB14) |

| 0FH   | PROM BYTE #15 (PB15) | PROM BYTE #15 (PB15) |

# TABLE 5. NEW PAGE 0 ADDRESS ASSIGNMENT FOR MEMORY MAP

| SA003 | READ               | WRITE              |

|-------|--------------------|--------------------|

| 00H   | Control 1          | Control 1          |

| 01H   | AT Detect          | Reserved           |

| 02H   | Reserved           | Reserved           |

| 03H   | Reserved           | Reserved           |

| 04H   | Reserved           | Reserved           |

| 05H   | Control 2          | Control 2          |

| 06H   | Reserved           | Reserved           |

| 07H   | Reserved           | Reserved           |

| 08H   | PROM BYTE #0 (PB0) | PROM BYTE #0 (PB0) |

| 09H   | PROM BYTE #1 (PB1) | PROM BYTE #1 (PB1) |

| 0AH   | PROM BYTE #2 (PB2) | PROM BYTE #2 (PB2) |

| 0BH   | PROM BYTE #3 (PB3) | PROM BYTE #3 (PB3) |

| 0CH   | PROM BYTE #4 (PB4) | PROM BYTE #4 (PB4) |

| 0DH   | PROM BYTE #5 (PB5) | PROM BYTE #5 (PB5) |

| 0EH   | PROM BYTE #6 (PB6) | PROM BYTE #6 (PB6) |

| 0FH   | PROM BYTE #7 (PB7) | PROM BYTE #7 (PB7) |

## 9.6 Write Network ID Back To EEPROM

The programmer has two approaches to store Network ID back to EEPROM. They are:

- 1. Store Network ID only

- 2. Store Configuration and Network ID at the same time

```

For case 1, the following procedure should be followed

exactly:

ID_STORE() {

Program_to_new_page_0();

// See Register description

if (necessary) Modify PROM Byte0 5();

Program_to_new_page_1();

// See Register description

write (HCMR, '16H');

// Issue IDWCMD

value = Read (HCMR) ;

while (value & IDWCMD) {

value = Read (HCMR);

wait ();

write (HCMR, '00H');

// Back to Normal mode

}

The following pseudo C code algorithm is for case 2:

ALL STORE () {

// See Regsiter description

Program_to_new_page 0 ( ) ;

if (necesary) Modify_PROM_BYTE0_7 ();

Program_to_new_Page_1();

// See Register description

write (HCMR, '20H');

// Enable All Write algorithm

EEPROM_STORE();

// Call EEPROM STORE subroutine}

```

Note:Only PROM byte 0-7 will be written back to EEPROM when ALL\_STORE() is issued.

#### 9.6.1 7 IO BASES SUPPORTED

300H (18H) -> 240H (22H) -> 280H (34H) -> 2C0H (46H) -> 320H (59H) -> 340H (64H) -> 360H (0BH) -> 300H -> (18H) (CYCLIC)

### 9.6.2 15 IO BASES SUPPORTED

300H (18H) -> 240H (22H) -> 280H (34H) -> 2C0H (46H) -> 320H (59H) -> 340H (6AH) -> 360H (7BH) -> 380H (8CH) -> 3A0H (9DH) -> 3C0H (AEH) -> 3E0H (BFH) -> 200H (C0H) -> 220H (D1H) -> 2A0H E5H) -> 2EH (07H) -> 300H (18H) (CYCLIC)

# 9.7 MULTIPLE LAN CARD AUTO CONFIGURATION

In case it is necessary for system to have more than one LAN cards plugged, the MX98905 provides a powerful solution to resolve "Multiple LAN card IO base conflict problem". It is not necessary for users to plug one LAN into the system then configure the IO base of the LAN card; then remove the first LAN card which is already configured and proceeds the second LAN card and so forth. Using MX98905, user can plug mutiple LAN cards into the system at the same time and then use software to configure these LAN cards for themselves.

To simply the mutiple LAN card auto configuration's operation, the MX98905 provides a bit, MULTI, in the HCMR. When this bit is set to 1, all LAN cards which use MX98905 will be forced to change to IO map (i.e. Novell NE2000 compaible). The "ID guess state machine" inside the MX98905 will be enables after MULTI bit is enabled. After that, software can write a certain value (will be explained in more detail in the following sub\_ section) into the MX98905 by consecutive 4 write to port 378H. The following shows an example (in 8088 assembly code) for writting this certain value into MX98905:

mov dx, 378

mov al, CERTAIN VALUER

out dx, al out dx, al out dx, al out dx, al out dx, al

When this certain value "hits" the 5th Network I.D. (the least significant byte), then IO base of this "ID hit" LAN card will be locked by MX98905 itself. i.e when writting 1 to AUTO, the IO base will not be changed.

By the way, when the guessed value is hit the Network I.D., a register call SIGNATURE (with value 78H, 'x') will be realeased by MX98905. If software can properly read the contents of SIGNATURE and ASR, then a conflit free IO base is found. If software can't access the value of SIGNATURE but ASR, then the guessed value is wrong. If software can't access the value of SIGNATURE nor ASR, then MX98905(s) is conflict with other add on cards. In case SIGNATURE can be accessed by software, then user can write 1 to LOCKE bit of **HCFR** through "NONCONFLICT IOBASE+08H". The IO base of this LAN card will be locked all the time to prevent it from jumpping to other IO base when AUTO is issued. See application notes or call SE/FAE if you have any questions.

To faciliate one to understand the "Mutiple LAN card auto configuration", an example is shown below: (Follow the steps shown in application note)

Condition: One LAN card with network ID 001111001001

: The second LAN card with network ID 0022220308

- 1. At the beginning, software first write AUTO. The IO base of both LAN card will be changed from their current IO bases to 300H.

- 2. Software guesses 00H, then write AUTO. Because the guessed I.D. (SID) hits the network I.D. on both LAN card, the IO bases of these two LAN cards will jump to 240H (assume software choose 7 IO bases)

- 3. Software guesses 01H, then issue AUTO. The software guessed I.D. (SID) hits the network I.D. (HID) of the first card, hence the IO base of the first card will stay at 240H and the IO base of the second card jumpped to 280H. Software can access "x" (78H,SIGNATURE register) from IO base 248H.

- 4. Software write 1 to LOCKE bit to lock the first card. 5. Software keep guessing and writing 1 to AUTO. Finally, a value, 08H, is guessed by software, and the IO base of card #2 jump to 240H. Because 240H is conflict with card #1, user can only access the value of ASR butSIGNATURE.

- 6. Software keep guessing and writing 1 to AUTO. The IO base of card #2 change from 240H to 280H.

- 7. User can access SIGNATURE and ASR from this IO base, the conflit\_free IO base for card #2 is found. Note: MX98905 uses one byte (ID byte #5) to determine SID is matched with HID or not, therefore, there is 1/256 posibility for 2 LAN cards get hit simultaneously.

The internal state machine will be reset after EEPROM\_STORE is finished.

This algorithm is preliminary. For actual implementation, user can contact with our FAE by calling 886-02-7191977 for details.

# 10. TWISTED-PAIR INTERFACE (TPI) MODULE

The TPI has five main logical functions:

- The Smart Squelch is responsible for determining when valid data is present on the differential receive inputs RXIP and RXIM

- The Collision function checks for simultaneous transmission and reception of data on the TXOP, TXOM, RXIP and RXIM.

- The Link Detector/Generator checks the integrity of the cable connecting the two twisted-pair MAUs.

- 4. The Jabber disables the transmitter if it attempts to transmit a longer-than-legal packet.

- 5. The TX Driver & Pre-emphasis transmit Manchester-encoded data to the twisted-pair network via the summing resistors and transformer/filter.

## 11. SMART SQUELCH

To make sure that impulse noise on the receive inputs will not be mistaken for a valid signal, the ENC carries out an intelligent receive squelch on the RX± differential inputs. The squelch circuitry uses a mix of amplitude and timing measurements.

Smart squelch checks the signal at the start of packet and any pulses that do not exceed the squelch level, either positive or negative, depending on polarity, is rejected. After this first squelch level is overcome the opposite squelch level must be exceeded within 150 ns. Finally, the signal goes beyond the original squelch level within a further 150 ns in order for the input waveform not to be rejected. The procedure entails the loss of at least three bits at the start of each packet.

When these conditions are satisfied a control signal will be generated to show the remainder of the circuitry that valid data is present. Then the smart squelch circuitry is reset.

Valid data is deemed present until either squelch level has not been generated for a time longer than 150 ns, which shows End of Packet. If good data is detected, the squelch levels are reduced to contain the noise effect which may lead to premature End-of-Packet detection.

#### 12. COLLISION

A collision is detected by the TPI module when the receive and transmit channels are active simultaneously. If the TPI is receiving when a collision is detected it is reported to the controller immediately. If, however, the TPI is transmitting when a collision is detected the collision is not reported until seven bits have been received while in the collision state. This prevents a collision from being reported incorrectly due to noise on the network. The signal to the controller remains for the duration of the collision.

Approximately 1ms after the transmission of each packet a signal called the Signal Quality Error (SQE) consisting of typically 10 cycles of 10 MHz is generated. This 10 MHz signal, also called the Heartbeat, ensures the continued functioning of the collision circuitry.

#### 13. LINK DETECTOR/GENERATOR

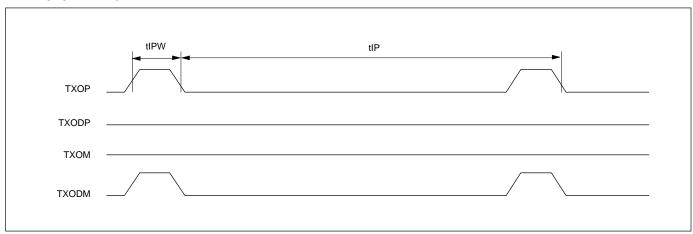

This is a timer circuit that generates a link pulse as shown in the 10BASE-T specification. With a width of 100 ns, the pulse is transmitted every 16 ms on the TXO+ output in the absence of transmit data.

The pulse checks the integrity of the connection to the remote MAU, and the link detection circuit checks for valid pulses from the remote MAU. The link detector will disable the transmit, receive, and collision detection functions if valid link pulses are not received.

To determine that a good twisted-pair link exists, the GDLNK output directly drives an LED; the LED will be on during normal conditions.

### 14. JABBER

Whenever the transmitter is active for greater than 52 ms, the jabber timer monitors the transmitter and disables the transmission. In this case, the transmitter is then disabled for the time that ENDEC module's internal transmit enable is asserted. This signal has to be deasserted for about 750 ms before the jabber re-enables the transmit outputs.

### 15. TRANSMIT DRIVER

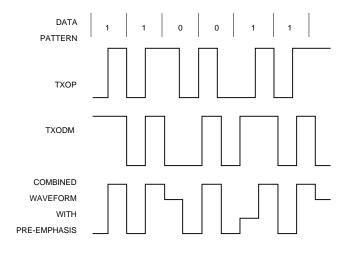

The transmitter has four signals, the true and complement Manchester-encoded data (TXOP and TXOM). These signals may be delayed by 50 ns (TXODP and TXODM).

These four signals are combined, TXOP with TXODM and TXOM with TXODP. Known as digital pre-emphasis, this process is required to compensate for the twisted-pair cable which acts like a low-pass filter and can greatly weaken the 10 MHz (50 ns) pulses of the Manchester-encoded waveform than the 5 MHz (100 ns) pulses.

A combination of these signals is shown below:

# 16. STATUS INFORMATION

This information is shown at the ENC on the CRS/RX, TXE/TX, COL and POL outputs as decribed in the pin description table. These outputs can drive status LEDs by means of an appropriate driver circuit.

Normally low, the POL output will be driven high when

seven consecutive link pulses or three consecutive link pulses having reversed polarity are detected. A wiring error at either end of the TPI cable can cause polarity reversal. Upon detection of this reversal the condition is latched and POL is asserted. Correcting this error is the TP1 and will also decode received data correctly, thus getting rid of the need to check the wiring error.

# 17. MANCHESTER ENCODER AND DIFFERENTIAL DRIVER

On the transformer's secondary, the differential transmit pair drives up to 50 meters of twisted-pair AUI cable. These outputs are source followers requiring two 270w pulldown resistors to ground.

#### 18. MANCHESTER DECODER

This decoder is composed of a differential receiver and a PLL to separate a Manchester-decoded data stream into internal clocks signals and data. When using the standard 78w transceiver drop cable, see that the differential input must be externally terminated with two 39w resistors connected in series. These resistors are optional in Thin Ethernet applications. A squelch circuit at the input rejects signals with levels less than -175 mV to prevent noise from triggering the decoder. And signals negative than -300 mV are decoded; data becomes valid within 5 bit times. The MX98905 may be able to take bit jitter up to 18 ns in the data that is received.

#### 19. COLLISION TRANSLATOR

If the Ethernet transceiver, when in AUI mode, detects a collision, it generates a 10 MHz signal to the differential collision inputs (CDP and CDM) of the MX98905. When these inputs are active, the MX98905 uses this signal to cancel its current transmission and reschedule another one.

The collision differential inputs are ended in the same way as the differential receive inputs. The squelch circuitry is also similar, rejecting pulses with levels less than -175 mV.

# 20. RECEIVE DESERIALIZER

The receive deserializer starts to work when the input

signal Carrier Sense is asserted. It allows incoming bits to be shifted into the shift register by the receive clock provided by the SNC (Serial Network Converter). The serial receive data is also routed to the CRC generator/checker to detect CRC code. The receive deserializer includes a synch detector that detects the SFD (Start of Frame Delimiter) to establish where byte boundaries within the serial bit stream are located, i.e., when a 1,1 bit sequence is detected, it begins to collect data. After every eight receive clocks, the byte-wide data is transferred to the 16-byte FIFO (two 8-byte FIFOs) alternatively and the receive byte count is incremented. The first six bytes after the SFD are checked for valid comparison by the Address Recognition Logic. If the address recognition Logic does not recognize the packet, the FIFO is cleared.

# 21. ADDRESS RECOGNITION LOGIC

The address recognition logic compares the destination address field (first 6 bytes of the received packet) with the physical address registers stored in the address register array, one byte at a time, by the 8th receive clock. If any one of the six bytes does not match the pre-programmed physical address, the protocol PLA rejects the packet. This means that the packet does not belong to the node. All multicast destination addresses are filtered using a hashing technique by latching the 6 most significant bits of the CRC generator. If the multicast address indexes a bit that has been set in the filter bit array of the multicast address register array, the packet is accepted. Otherwise, it is rejected by the Protocol PLA. Each destination address is also checked for all 1's, which is the reserved broadcast address.

## 22. PACKET TRANSMISSION

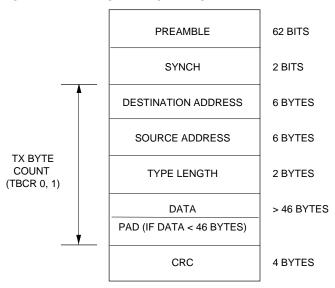

A complete transmit packet consists of Preamble, Synch, Data, and CRC fields. The data field is a contiguous assembled packet of Destination Address. Source Address, Length Field, and Data with the format are shown below. During transmit, Page Start Address Register (TPSR) and the Transmit Byte Count Registers (TBCR0,1), control the DMA transfer. As a transmit command is issued to ENC, the packet of data in buffer memory pointed 0 by these registers will be moved into the FIFO. The ENC will generate and append the preamble, synch and CRC fields. In

addition, if transmitting data is smaller than 46 bytes, the packet must be padded to a minimum size of 64 bytes. The programmer is responsible for adding and stripping pad bytes.

#### **GENERAL TRANSMIT PACKET FORMAT**

# 23. CONDITIONS REQUIRED TO BEGIN TRANS-MISSION

To initiate transmission of a packet, the TPSR (Transmit Page Start Register) and TBCR0, TBCR1 (Transmit Byte Count Registers) must be initialized and the TXP bit in the Command Register must be set. The ENC will start to prefetch transmit data from memory, if no reception is currently receiving. Three conditions must be met before transmission:

- 1. The Interframe Gap Timer has timed out the first 6.4ms of the Interframe Gap.

- 2. At least one byte has entered the FIFO, which means that burst transfer has begun.

- 3. If collision occurs in the ENC, the backoff timer must expire before retransmit.

If carrier sense is asserted before a byte has been loaded into the FIFO, the ENC will become a receiver.

## 24. COLLISION RECOVERY

If transmission has collided with another station, the buffer management logic, which monitors the transmit circuitry will reset the FIFO and restore the Transmit DMA pointers for retransmission of the packet. When collision is detected, the COL bit in TSR will be set and the NCR (Number of Collisions Register) will be incremented. If each of the 15 retransmissions results in a collision, the transmission will be terminated and the ABT bit in the TSR will be set. If excessive collisions (i.e., 16 consecutive collisions) are encountered, NCR reads as zeros and transmission is aborted.

### 25. TRANSMIT PACKET ASSEMBLY FORMAT

The following diagrams show the format for assembling packets before they are transmitted for different byte- ordering schemes. The various formats are selected in the Data Configuration Register.

DA = Destination Address SA = Source Address T/L = Type/Length Field

| BIT D | D15 D8 | 3 D7 D0 |

|-------|--------|---------|

|       | DA1    | DA0     |

|       | DA3    | DA2     |

|       | DA5    | DA4     |

|       | SA1    | SA0     |

|       | SA3    | SA2     |

|       | SA5    | SA6     |

|       | T/T1   | T/L0    |

|       | DATA1  | DATA0   |

BOS = 0, WTS -1 in Data Configuration Register. This format used with Series 32000, 808X-type processors.

| BIT D | 15    | D8 D7 | D0 |

|-------|-------|-------|----|

|       | DA0   | DA1   |    |

|       | DA2   | DA3   |    |

|       | DA4   | DA5   |    |

|       | SA0   | SA1   |    |

|       | SA2   | SA3   |    |

|       | SA4   | SA5   |    |

|       | T/L0  | T/L1  |    |

|       | DATA0 | DATA  | .1 |

BOS = 1, WTS = 1 in Data Configuration Register. This format is used with 68000-type processors.

| DA0 |

|-----|

| DA1 |

| DA2 |

| DA3 |

| DA4 |

| DA5 |

| SA0 |

| SA1 |

| SA2 |

| SA3 |

|     |

BOS = 0, WTS = 1 in data Configuration Register. This format is used with general 8-bit CPUs.

# 26. PHYSICAL ADDRESS REGISTERS (PAR0-PAR5)

The physical address registers are used to compare the destination address of incoming packets for rejecting or accepting packets. It compares physical addresses in PAR0-PAR5 with incoming data one byte at a time. The bit assignment shown below relates the sequence in PAR0-PAR5 to the bit sequence of the received packet.

|      | D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0   |  |

|------|------|------|------|------|------|------|------|------|--|

| PAR0 | DA7  | DA6  | DA5  | DA4  | DA3  | DA2  | DA1  | DA0  |  |

| PAR1 | DA15 | DA14 | DA13 | DA12 | DA11 | DA10 | DA9  | DA8  |  |

| PAR2 | DA23 | DA22 | DA21 | DA20 | DA19 | DA18 | DA17 | DA16 |  |

| PAR3 | DA31 | DA30 | DA29 | DA28 | DA27 | DA26 | DA25 | DA24 |  |

| PAR4 | DA39 | DA38 | DA37 | DA36 | DA35 | DA34 | DA33 | DA32 |  |

| PAR5 | DA47 | DA46 | DA45 | DA44 | DA43 | DA42 | DA41 | DA40 |  |

# **DESTINATION ADDRESS**

SOURCE

| P/S | DA0 | DA1 | DA2 | DA3 |  | DA46 | DA47 | SA0 |  |

|-----|-----|-----|-----|-----|--|------|------|-----|--|

|-----|-----|-----|-----|-----|--|------|------|-----|--|

NOTE: P/S = Preamble, Synch DA0 = Physical/Multicast Bit

## **REGISTER ADDRESS MAPPING**

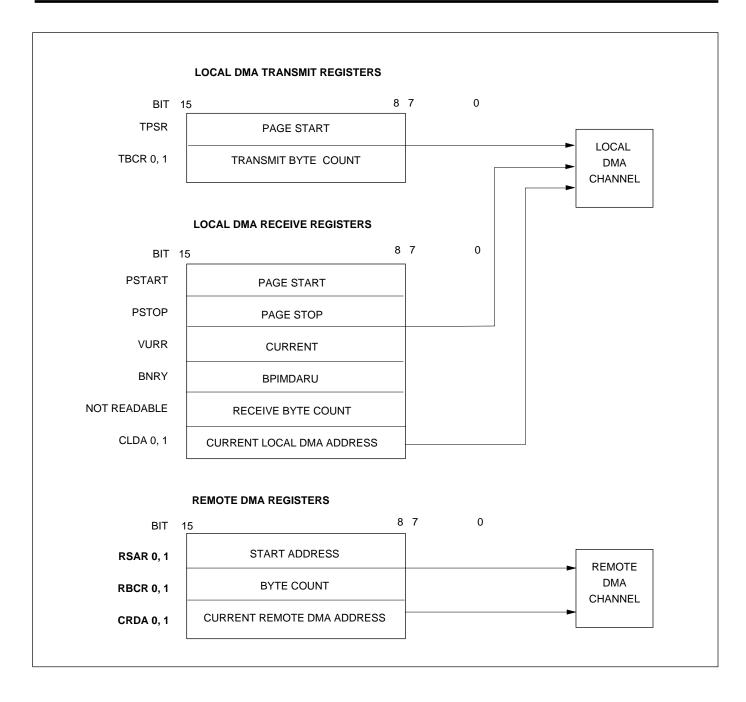

# 27. DIRECT MEMORY ACCESS CONTROL (DMA)

The DMA capabilities of the ENC greatly simplify use of the MX98905 in typical configuration. The local DMA channel transfers data between FIFO, which is inside the ENC, and memory which is outside the ENC. There are two kinds of local DMA type: Local DMA Read and Local DMA Write. Local DMA Read moves data from memory into FIFO on transmission. Should a collision occur (up to 15 times), the packet is retransmitted with no processor intervention. Local DMA Write transfers data from FIFO to memory on reception.

A remote DMA channel is also provided on the ENC to accomplish transfers between a buffer memory and a system memory whenever the I/O map board design is required. The two DMA channels (local DMA and remote DMA) can alternatively be combined to form a single 32-bit address with 8- or 16-bit data.

### 28. DUAL DMA CONFIGURATION

Network activity is isolated on a local bus, where the ENC's local DMA channel performs burst transfers between the buffer ring and the ENC's FIFO. The remote DMA transfers data between the buffer ring and the host memory by means of a bi-directional I/O port. Meanwhile, remote DMA provides local addressing capability and is used as a slave DMA by the host. Host side addressing must be provided by a host DMA or the CPU. The ENC allows Local and Remote DMA operations to be interleaved because the ENC takes care of the bus arbitration problem itself.

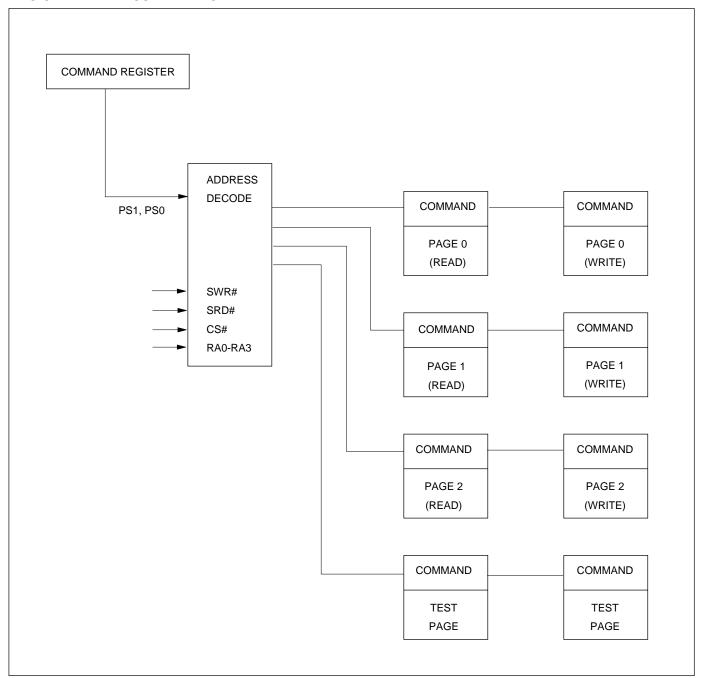

## 29. INTERNAL REGISTERS

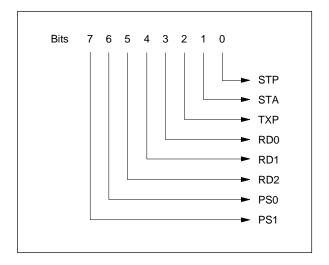

All internal registers are mapped into three pages and selected by two bits, PS1 and PS0, of Command Register. Input pins RA0-RA3 are used to address these internal registers which are 8-bit wide and are commonly accessed during ENC register read/write operation. For user's convenience, registers that are commonly accessed during ENC operation are mapped into page 0. Page 1 registers are used primarily for initialization while Page 2 registers are used for diagnostics. Partitioned registers make one write/read cycle possible for accessing those commonly used registers.

# **REGISTER DESCRIPTIONS**

# 1. ENHANCED FEATURE NEW PAGE REGISTER ADDRESS ASSIGNMENT

# NEW PAGE 1 ADDRESS ASSIGNMENT FOR I/O MAP

| SA003 | READ                  | WRITE                 |

|-------|-----------------------|-----------------------|

| 00H   | Reserved              | Reserved              |

| 01H   | Reserved              | Reserved              |

| 02H   | Reserved              | Reserved              |

| 03H   | Reserved              | Reserved              |

| 04H   | Reserved              | Reserved              |

| 05H   | Reserved              | Reserved              |

| 06H   | Reserved              | Reserved              |

| 07H   | Reserved              | Reserved              |

| 08H   | Signature (x, 78H)    | Reserved              |

| 09H   | Hidden Config. (HCFR) | Hidden Config. (HCFR) |

| 0AH   | Hidden Command (HCMR) | Hidden Command (HCMR) |

| 0BH   | Reserved              | Reserved              |

| 0CH   | Configuration C (CC)  | Configuration C (CC)  |

| 0DH   | Reserved              | Reserved              |

| 0EH   | AutoStatus Reg. (ASR) | Reserved              |

| 0FH   | Reserved              | Reserved              |

# NEW PAGE 1 ADDRESS ASSIGNMENT FOR MEMORY MAP

| SA04 | READ                  | WRITE                 |

|------|-----------------------|-----------------------|

| 10H  | Reserved              | Reserved              |

| 11H  | Reserved              | Reserved              |

| 12H  | Reserved              | Reserved              |

| 13H  | Reserved              | Reserved              |

| 14H  | Reserved              | Reserved              |

| 15H  | Reserved              | Reserved              |

| 16H  | Reserved              | Reserved              |

| 17H  | Reserved              | Reserved              |

| 18H  | Signature (x, 78H)    | Reserved              |

| 19H  | Hidden Config. (HCFR) | Hidden Config. (HCFR) |

| 1AH  | Hidden Command (HCMR) | Hidden Command (HCMR) |

| 1BH  | Reserved              | Reserved              |

| 1CH  | Configuration C (CC)  | Configuration C (CC)  |

| 1DH  | Reserved              | Reserved              |

| 1EH  | AutoStatus Reg. (ASR) | Reserved              |

| 1FH  | Reserved              | Reserved              |

Data Transfer ports and Reset port are always accessible no matter what the value of NPGEN and PGSEL is in I/O map design.

# 2. ENHANCED FEATURE REGISTERS

# 2.1 HIDDEN COMMAND REGISTER (R/W) (HCMR)

This register controls all the functions provided in enhanced mode. It can always be accessed by consecutive 2 writes to port 278H, followed by 2 consecutive 2 writes to port 378H, i.e., write ports:  $278H \times 278H \times 378H \times 378H \times 378H \times 1000$  (when I/O Base not sure)

After the I/O base is determined (see functional description), this register can be accessed by one I/O instruction using the address assignment shown in provious section.

**NOTE:** Don't write this register through Base+0AH/Base+1AH (I/O/MEM) except it is confirmed that I/O base does not conflict with other ADD\_on card.

# HIDDEN COMMAND REGISTER (R/W) (HCMR)

| SYMBOL      | BIT   | DESCRIPTION                                                                            |

|-------------|-------|----------------------------------------------------------------------------------------|

| HCFRE       | D0    | Register HCFRE Enable. Power on low.                                                   |

|             |       | 0 : Disable HCFR.                                                                      |

|             |       | 1: Enable HCFR. When user issues EESTORE in Configuration Register B,                  |

|             |       | contents in figh byte of OFH of EEPROM. Whiih is reserved at                           |

| NPGEN,PGSEL | D2,D1 | New Page Enable/Page Select. Power on low.                                             |

|             |       | 0X: Normal Mode. User can access controller's internal registers.                      |

|             |       | 10: User can access IDPROM through IOBASE + 00OFH in I/O map. See                      |

|             |       | table 4 for your reference.                                                            |

|             |       | 11: New Page 1 selectsd. User can access HCMR, CC, ASR and                             |

|             |       | SIGNATURE. See "New Page 1 address assignment for I/O map" and "New                    |

|             |       | Page 1 address assignment for Memory map " for more detail information.                |

|             |       | Make sure set NPGEN to 0 before normal operation. Data port and Reset port             |

|             |       | in I/O map are accessible no matter what the value of NPGEN and PGSEL                  |

|             |       | are.                                                                                   |

| AUTO        | D3    | Auto Jump to Next I/O base. Power on low.                                              |

| 7.0.0       | 20    | 0 : Write a 0 to this bit has no effect.1 : Write an 1 to this bit will cause I/O base |

|             |       | auto jump follow the sequence described in section 9.5 Auto Configuration.             |

|             |       | In multiple LAN cards auto configuration's application (see section 9.5), if SID       |

|             |       | hits the HID, then write an 1 to this bit has no effect. The first time writing an     |

|             |       | -                                                                                      |

|             |       | 1 to AUTO will cause IO base change to 300H no matter what the current IO              |

|             |       | base is.                                                                               |

|             |       | Whenever AUTO is issued, the value of IOAD20 in CA and PAGE in HCFR                    |

|             |       | will be updated automatically by the state machine inside the MX98905.                 |

|             |       | Either 7 or 15 IO bases should be determined before AUTO is issued to                  |

|             |       | prevent the internal state machine getting confused. Any IORDL signal                  |

| IDWOMD      | D.4   | activates will reset this bit.                                                         |

| IDWCMD      | D4    | IDPROM Write Command. Power on low.                                                    |

|             |       | 0 : Write a 0 to this bit has no effect.                                               |

|             |       | 1 : The MX98905 will write the first 4 words of PROM data (Net work I.D.,              |

|             |       | Boardtype and Checksum) back to EEPROM when this bit is set. When the                  |

|             |       | operation is completed, this bit will be reset by MX98905 itself. Don't write          |

|             |       | an 1 to this bit and EESTORE of CB simultaneously, this will cause internal            |

|             |       | state machine malfunction.                                                             |

| ALLWR       | D5    | Write CA, CB, CC, HCFR, The entire PROM content back to EEPROM.                        |

|             |       | Power on low.                                                                          |

|             |       | 0 : Only CA, CB, CC and HCFR are written back to EEPROM when                           |

|             |       | EESTORE bit of CB is set to 1.                                                         |

|             |       | 1 : CA, CB, CC, HCFR, and the entire PROM content will be writtenback to               |

|             |       | EEPROM when EESTORE bit is set to 1. If new Network I.D. is necessary,                 |

|             |       | make sure I.D. is updated before this bit-is set and before EESTORE bit is             |

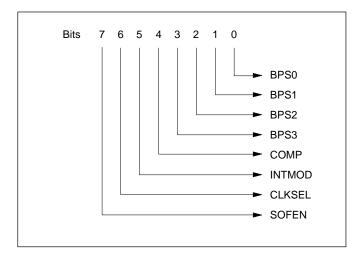

|             |       | set to 1, the following write sequence will be followed after EESTORE bit is set       |