## MX98902A

FOR TWISTED-PAIR

## FEATURES

- Compatible with IEEE 802.3 CSMA/CD standard Ethernet, Cheapernet, and Twisted-Pair (10 BASET)

- Two 16-bit DMA channels

- 16-byte internal FIFO with programmable threshold

- Network statistics storage

- 3 levels of loopback

- Independent system and network clocks

- CMOS technology, 84-pin PLCC or 100-pin PQFP package

ETHERNET NETWORK CONTROLLER

NS DP83902 compatible

### **GENERAL DESCRIPTION**

The MX98902 is designed for easy implementation of CSMA/CD local area networks, which include Ethernet (10BASE5), Thin Ethernet (10BASE2), and Twisted-pair Ethernet (10BASE-T). The Media Access Control (MAC) and Encode-Decode (ENDEC) are provided with an AUI interface. The 10BASE-T transceiver functions according to the IEEE 802.3 standards, and the MX98902 10BASE-T transceiver operates in compliance with the IEEE standard.

The MX98902's functional block consists of the receiver, transmitter, collision, heartbeat, loopback, jabber, and link integrity blocks. When combined with equalization resistors, the transceiver transmits or receives filters, and pulse transformers provide physical interface from the MX98902's ENDEC module and the twisted-pair medium.

Manchester encoding and decoding is made possible through the integrated ENDEC module by means of a differential transceiver and phase lock loop decoder at 10 Mbit/sec. Collision detect translator and diagnostic loopback capability are included in this process. Interfacing directly with the transceiver module, the ENDEC module also provides a fully IEEE compliant AUI (Attachment Unit Interface) to connect with other media transceivers.

The Media Access Control function, provided by the Ethernet Network Control (ENC) module, effects an efficient packet transmission and reception control through unique dual DMA channels and an internal FIFO. To lessen board cost and area overheads, bus arbitration and memory control logic are integrated.

Designed for easy interface with other transceivers by means of the AUI interface, the MX98902 provides a thorough single chip solution for 10BASE-T IEEE 802.3

#### network.

Constraints of CMOS processing require that isolation, whether capacitive or inductive, be used at the AUI differential signal interface for 10BASE5 and 10BASE2 applications.

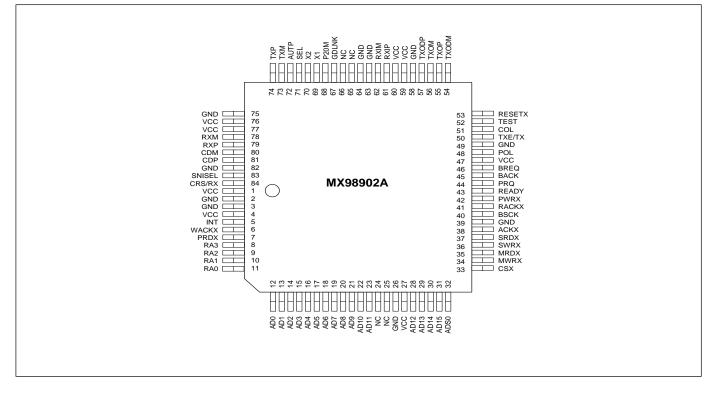

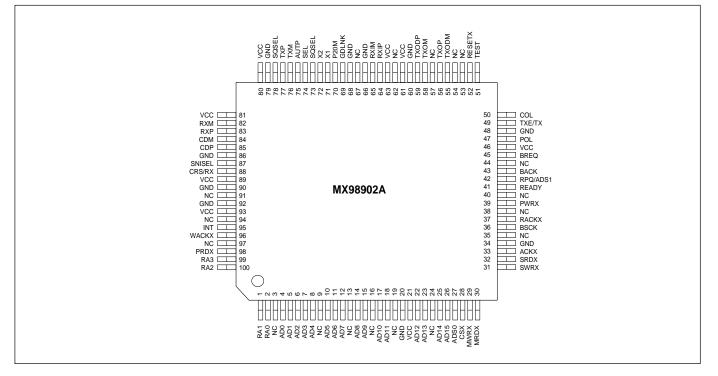

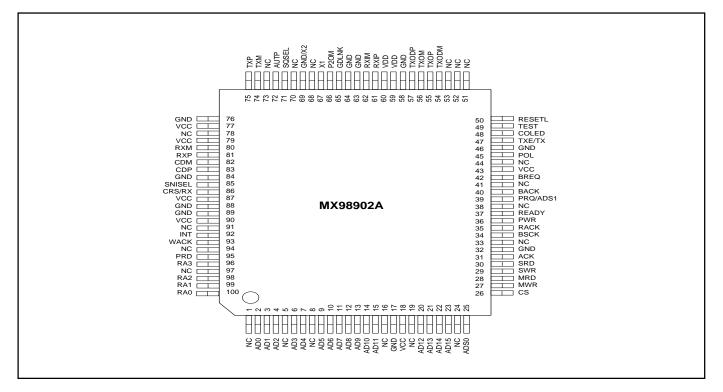

## **PIN CONFIGURATIONS**

#### **84-PIN PLCC**

#### **100-PIN PQFP**

## **100-PIN SQFP**

## **PIN DESCRIPTIONS**

### A. BUS INTERFACE PINS

| SYMBOL   | PIN TYPE |                                                   | N NUME<br>PLCC |                             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|----------|---------------------------------------------------|----------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD0-AD15 | I/O, Z   | 4-8,<br>10-12<br>14,15<br>17,18<br>22,23<br>25,26 | 12-23<br>28-31 | 2-4<br>6-7<br>9-15<br>20-23 | <ul> <li>MULTIPLEXED ADDRESS/DATA BUS: Registeaccess,wit<br/>DMA inactive, CSX low and ACKX returned fromMX98902,<br/>pins AD0-AD7 are used to read/write register data.<br/>AD8-AD15 float during I/O transfers. SRDX, SWRX pins an<br/>used to select direction of transfer.<br/>Bus Master with BACK input asserted.<br/>During T1 or memory cycle AD0-AD15 contain address.<br/>During T2, T3, T4 AD0-AD15 contain data (word transfer<br/>mode).<br/>During T2, T3, T4 AD0-AD7 contain data; AD8-AD15 contai<br/>address (bytetransfer mode).</li> <li>Direction of transfer is indicated by MX98902 on MWR2<br/>MRDX lines.</li> </ul> |

| ADS0     | I/O, Z   | 27                                                | 32             | 25                          | ADDRESS STROBE 0: Input with DMA inactive and CS<br>low, latches RA0-RA3 inputs on falling edge. If high, da<br>present on RA0-RA3 will flow through latch.<br>Output when Bus Master latches addresses bits (A0-A15)<br>external memory during DMA transfers.                                                                                                                                                                                                                                                                                                                                                                               |

| CSX      | Ι        | 28                                                | 33             | 26                          | CHIP SELECT: Chip Select places controller in slave more<br>for µp access to internal registers. Must be val<br>through data portion of bus cycle. RA0-RA3 are used<br>select the internal register. SWRX and SRDX select direct<br>tion of data transfer.                                                                                                                                                                                                                                                                                                                                                                                   |

| MWRX     | O, Z     | 29                                                | 34             | 27                          | <b>MASTER WRITE STROBE</b> : Strobe for DMA transfers, a tive low during write cycles (T2, T3, TW) to buffer memor Rising edge coincides with the presence of valid output dat TRI-STATE until BACK asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| MRDX     | O,Z      | 30                                                | 35             | 28                          | <b>MASTER READ STROBE</b> : Strobe for DMA transfers, activity during read cycles (T2, T3, TW) to buffer memory. Inp data must be valid on rising edge of MRDX. TRI-STAT until BACK asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SWRX     | I        | 31                                                | 36             | 29                          | <b>SLAVE WRITE STROBE</b> : Strobe from CPU to write a internal register selected by RA0-RA3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SRDX     | Ι        | 32                                                | 37             | 30                          | <b>SLAVE READ STROBE</b> : Strobe from CPU to read an intend nal register selected by RA0-RA3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| АСКХ     | 0        | 33                                                | 38             | 31                          | <b>ACKNOWLEDGE</b> : Active low when MX98902 grants a cess to CPU. Used to insert WAIT states to CPU un MX98902 is synchronized for a register read or write oper tion.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RA0-RA3  | Ι        | 99,100<br>1,2                                     | ) 8-11         | 96<br>98-100                | <b>REGISTER ADDRESS</b> : These four pins are used to select register to be read or written. The state of these inputs ignored when the MX98902 is not in slave mode (CSX high                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PRDX     | 0        | 98                                                | 7              | 95                          | <b>PORT READ</b> : Enables data from external latch onto loc<br>bus during a memory write cycle to local memory (remo<br>write operation). This allows asynchronous transfer of da<br>from the system memory to local memory.                                                                                                                                                                                                                                                                                                                                                                                                                |

## PIN DESCRIPTIONS (Continued) A. BUS INTERFACE PINS

| SYMBOL    | PIN TYPE | PIN NUMBER<br>PQFP PLCC SQFP |    |    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|-----------|----------|------------------------------|----|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| WACKX     | I        | 96                           | 6  | 93 | WRITE ACKNOWLEDGE: Issued from system to ENC to ind cate data has been written to the external latch. The ENC w begin a write cycle to place the data in local memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| INT       | 0        | 95                           | 5  | 92 | <b>INTERRUPT</b> : Indicates that the MX98902 requires CPU attention after reception, transmission, or completion of DMA transfers. The interrupt is cleared by writing to the ISR. All interruptive are maskable.                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| RESETX    | I        | 52                           | 53 | 50 | <b>RESET:</b> Reset is active low and places the MX98902 in a res<br>mode immediately; no packets are transmitted or received to<br>the ENC until STA bit is set. Affects Command Register, Inter<br>rupt Mask Register, Data Configuration Register and Transm<br>Configuration Register. The MX98902 will execute reset with<br>10 BSCK cycles.                                                                                                                                                                                                                                                                                   |  |  |  |

| BREQ      | 0        | 45                           | 46 | 42 | <b>BUS REQUEST</b> : Bus Request is an active high signal used request the bus for DMA transfers. This signal is automatical generated when the FIFO needs servicing.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| BACK      | I        | 43                           | 45 | 40 | <b>BUS ACKNOWLEDGE</b> : Bus Acknowledge is an active hig<br>signal that the CPU has granted the bus to MX98902. If immed<br>ate bus access is desired, BREQ should be tied to BACI<br>Tying BACK to VCC will result in a deadlock.                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| PRQ, ADS1 | O, Z     | 42                           | 44 | 39 | <ul> <li>PORT REQUEST/ADDRESS STROBE 1: 32-bit mode: If LA is set in the Data Configuration Register, this line is programmed as ADS1; it is used to strobe addresses A16-A31 into extern latches. (A16-A31 are the fixed addresses stored in RSAR RSAR1.) ADS1 will remain at TRI-STATE until BACK is received.</li> <li>16-bit mode: If LAS is not set in the Data Configuration Register, this line is programmed as PRQ and is used for Remo DMA Transfers. In this mode PRQ will be a standard log output.</li> <li>Note: This line will power up as TRI-STATE until the Data Configuration Register is programmed.</li> </ul> |  |  |  |

| READY     | I        | 41                           | 43 | 37 | <b>READY</b> : This pin is set high to insert wait states until a DM transfer. The MX98902 will sample this signal at T3 during DM transfers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| PWRX      | 0        | 39                           | 42 | 36 | <b>PORT WRITE</b> : Strobe used to latch data from the MX98902 in external latch for transfer to host memory during remote real transfers. The rising edge of PWRX coincides with the presence of valid data on the local bus.                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| RACKX     | I        | 37                           | 41 | 35 | <b>READ ACKNOWLEDGE:</b> Indicates that the system DMA host CPU has read the data placed in the external latch by th MX98902. The MX98902 will begin a read cycle to update th latch MX98902.                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

## PIN DESCRIPTIONS (Continued)

## **B. NETWORK INTERFACE PINS**

| SYMBOL PIN TYPE         |     | PIN NUMBER<br>PQFP PLCC SQFP |                |                | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|-------------------------|-----|------------------------------|----------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| POL                     | 0   | 47                           | 48             | 45             | <b>POLARITY</b> : A TTL/MOS active high output. This signal is<br>normally low. When the TPI module detects seven consecu-<br>tive link pulses or three consecutive received packets with<br>reversed polarity POLED is asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| TXE/TX                  | 0   | 49                           | 50             | 47             | <b>TRANSMIT ENABLE/TRANSMIT</b> : A TTL/MOS active high output. It is asserted for approximately 50 ms whenever the MX98902 transmits data in either the AUI or TPI modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| TEST                    | I   | 51                           | 52             | 49             | <b>FACTORY TEST INPUT</b> : Used to check the chip's interna function. This should be tied low during normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| TXODM, TXO<br>TXOM, TXO |     | O<br>58,59                   | 55,56<br>56,57 | 54,55<br>56,57 | <b>TWISTED-PAIR TRANSMIT OUTPUTS</b> : These high drive<br>CMOS-level outputs are resistively combined external to the<br>chip to produce a differential output signal with equalization<br>to compensate for inter-symbol interference (ISI) on the<br>twisted-pair medium.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| RXIP, RXIM              | I   | 64,65                        | 61,62          | 61,62          | <b>TWISTED-PAIR RECEIVE INPUTS:</b> These inputs feed a differential amplifier which passes valid data to the ENDEC module.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| GDLNK                   | I/O | 69                           | 67             | 65             | <b>GOOD LINK</b> : This pin has a dual input and output functions<br>The function is latched by the MX98902 on the rising edge o<br>the Reset signal i.e.: on the chip returning to normal opera<br>tion after reset. As an output, this pin is configured as ar<br>open drain N-channel device and is suitable for driving ar<br>LED. It will be latched as output on removal of chip reset i<br>connected to an LED or left open circuit. Under norma<br>conditions (the twisted-pair link is not broken) the output will<br>be low, and the LED will be lit. The open drain output will be<br>switched off if the twisted-pair link has been detected to be<br>green. This output will be pulled high in AUI mode by ar<br>internal resistor of approximately 15K $\Omega$ . When this pin<br>which has an internal pull-up resistor to VDD, is tied low, i<br>becomes an input and the link integrity checking is disabled. |  |  |  |

| P20M                    | 0   | 70                           | 68             | 66             | <b>20 MHz</b> : This is a TTL/MOS-level signal. It is a buffered version of the oscillator X2. It is suitable to drive externa logic, if a crystal is applied to X1 and X2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| X1                      | I   | 71                           | 69             | 67             | EXTERNAL OSCILLATOR INPUT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| X2                      | I   | 72                           | 70             | 69             | X2: This pin should normally be connected to ground. It is<br>possible to use a crystal oscillator using X1 and X2 if certain<br>precautions are taken.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| SQUEL                   | 1   | 73                           | -              | 71             | <b>TPI SQUELCH SELECT</b> : This pin selects the TPI module<br>input squelch thresholds. When tied low, the input squelch<br>threshold on the RXIP, RXIM input complies to 10BASE-T<br>specification. When set high, the RXIP and RXIM input oper-<br>ates with reduced squelch levels, allowing its use with longer<br>lengths of cable or cable with higher losses. Internal pul<br>down.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

## PIN DESCRIPTIONS (Continued) B. NETWORK INTERFACE PINS

| SYMBOL   | PIN TYPE | PIN NUMBER<br>PQFP PLCC SQFP |       |       | DESCRIPTION                                                                                                                                                                                                                   |  |  |  |

|----------|----------|------------------------------|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SEL      | I        | 74                           | 71    | _     | <b>MODE SELECT</b> : When high, TXP and TXM are the same voltage when idle. If low, TXP is positive with respect to TXM when idle, at the transformer's primary.                                                              |  |  |  |

| AUTP     | I        | 75                           | 72    | 72    | <b>AUI/TPI SELECT</b> : A TTL level active high input that selects either the AUI interface or the TPI module for interface with the ENDEC module. When high, the AUI is selected. When low, the TPI is selected.             |  |  |  |

| TXM, TXP | 0        | 76,77                        | 73,74 | 74,75 | AUI TRANSMIT OUTPUT: Differential driver which sends the encoded data to the transceiver. The outputs are source followers which require $270\Omega$ pulldown resistors.                                                      |  |  |  |

| RXM, RXP | I        | 82,83                        | 78,79 | 80,81 | <b>AUI RECEIVE INPUT:</b> Differential receive input pair from the transceiver.                                                                                                                                               |  |  |  |

| CDM, CDP | I        | 84,85                        | 80,81 | 82,83 | <b>AUI COLLISION INPUT:</b> Differential collision pair input from the transceiver.                                                                                                                                           |  |  |  |

| SNISEL   | I        | 87                           | 83    | 85    | <b>FACTORY TEST INPUT</b> : For normal operation tied to VCC. When low, it enables the ENDEC module to be tested independently of the MX98902.                                                                                |  |  |  |

| CRS/RX   | 0        | 88                           | 84    | 86    | <b>CARRIER SENSE/RECEIVE:</b> A TTL/MOS-level active high signal. It is asserted for approximately 50 ms whenever valid transmit or receive data is detected while in AUI mode or receive data is detected while in TPI mode. |  |  |  |

| COL      | 0        | 50                           | 51    | 48    | <b>COLLISION</b> : A TTL/MOS active high output. It is asser<br>for approximately 50ms whenever the MX98902A detect<br>collision in either the AVI or TPI modes.                                                              |  |  |  |

## **PIN DESCRIPTIONS (Continued)**

## C. POWER SUPPLY PIN (DIGITAL)

| SYMBOL | PIN TYPE | PIN NUMBER<br>PQFP PLCC SQFP |             |              | DESCRIPTION                                                   |

|--------|----------|------------------------------|-------------|--------------|---------------------------------------------------------------|

| VCC    |          | 21,46<br>89                  | 1, 27<br>47 | 18,43<br>87  | POSITIVE 5V SUPPLY PINS.                                      |

| GND    |          | 20,90                        | 2, 26       | 17,32        | NEGATIVE (GROUND) SUPPLY PINS: It is suggested that           |

|        |          | 34,48<br>68                  | 39,49<br>64 | 46 ,64<br>88 | a decoupling capacitor be connected between VCC and GND pins. |

## D. POWER SUPPLY PINS (ANALOG)

| SYMBOL | PIN TYPE |      |      |      | DESCRIPTION                                                                                                                              |  |  |  |  |

|--------|----------|------|------|------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|        |          | PQFP | PLCC | SQFP |                                                                                                                                          |  |  |  |  |

| VCC    |          | 93   | 4    | 90   | VCO 5V SUPPLY PIN: Care should be taken to reduce<br>noise on this pin as it supplies power to the analog VCC to<br>the Phase Lock Loop. |  |  |  |  |

| GND    |          | 92   | 3    | 89   | VCO GROUND SUPPLY PIN: Care should be taken to reduce noise on this pin as it supplies ground to the analog VCC to the Phase Lock Loop.  |  |  |  |  |

| VCC    |          | 63   | 60   | 60   | <b>TPI RECEIVE 5V SUPPLY:</b> Power pin supplies 5V to the Twisted-pair Interface Receiver.                                              |  |  |  |  |

| GND    |          | 66   | 63   | 63   | <b>TPI RECEIVE GROUND:</b> Ground pin for the Twisted-pai Interface Receiver.                                                            |  |  |  |  |

| VCC    |          | 61   | 59   | 59   | <b>TPI TRANSMIT 5V SUPPLY</b> : Power pin supplies 5V to the Twisted-pair Interface Transmitter.                                         |  |  |  |  |

| GND    |          | 60   | 58   | 58   | <b>TPI TRANSMIT GROUND</b> : Ground pin for the Twisted-pai Interface Transmitter.                                                       |  |  |  |  |

| VCC    |          | 81   | 77   | 79   | <b>AUI RECEIVE 5V SUPPLY:</b> Power pin supplies 5V to the AUI Interface Receiver.                                                       |  |  |  |  |

| GND    |          | 86   | 82   | 84   | AUI RECEIVE GROUND: Ground pin for the AUI Interface Receiver.                                                                           |  |  |  |  |

| VCC    |          | 80   | 76   | 77   | AUI TRANSMIT 5V SUPPLY: Power pin supplies 5V to AU Interface Transmitter.                                                               |  |  |  |  |

| GND    |          | 79   | 75   | 76   | AUI TRANSMIT GROUND: Ground pin for the AUI Interface Transmitter.                                                                       |  |  |  |  |

## PIN DESCRIPTIONS (Continued)

## E. NO CONNECTION

| SYMBOL PIN T | YPE PIN NUMBER<br>PQFP PLCC S                                                   |                                                                           |

|--------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| NC           | 16,19 65,66 1<br>24,35 2<br>38,40 3<br>44,53 2<br>54,57 5<br>62,67 6<br>78,91 7 | ,5,8<br>6,19<br>4,33<br>8,41<br>4,51<br>2,53<br>8,70<br>3,78<br>1,94<br>7 |

## FUNCTIONAL DESCRIPTION

### TWISTED-PAIR INTERFACE (TPI) MODULE

The TPI has five main logical functions:

- 1. The Smart Squelch, responsible for determining when valid data is present on the differential receive inputs (RXI±)

- 2. The Collision function checks for simultaneous transmission and reception of data on the TXO± and RXI± pins.

- 3. The Link Detector/Generator checks the integrity of the cable connecting the two twisted-pair MAUs.

- 4. The Jabber disables the transmitter if it attempts to transmit a longer than legal packet.

- 5. The TX Driver & Pre-emphasis transmit Manchester encoded data to the twisted-pair network via the summing resistors and transformer/filter.

### SMART SQUELCH

To make sure that impulse noise on the receive inputs will not be mistaken for a valid signal, the ENC carries out an intelligent receive squelch on the  $RX\pm$  differential inputs. The squelch circuitry uses a mix of amplitude and timing measurements to gauge whether the data on the twisted-pair inputs is valid.

Smart squelch checks the signal at the start of packet and any pulses that do not exceed the squelch level, either positive or negative, depending on polarity, is rejected. After this first squelch level is overcome the opposite squelch level must be exceeded within 150 ns. Finally, the signal goes beyond the original squelch level within a further 150 ns in order for the input waveform not to be rejected. The procedure entails the loss of at least three bits at the start of each packet.

When these conditions are satisfied a control signal will be generated to show the remainder of the circuitry that valid data is present. Then the smart squelch circuitry is reset.

Valid data is deemed present until either squelch level has not been generated for a time longer than 150 ns,

which shows End of Packet. If good data is detected, the squelch levels are reduced to contain the noise effect which may lead to premature End of Packet detection.

### COLLISION

A collision is detected by the TPI module when the receive and transmit channels are active simultaneously. If the TPI is receiving when a collision is detected it is reported to the controller immediately. If, however, the TPI is transmitting when a collision is detected the collision is not reported until seven bits have been received while in the collision state. This prevents a collision being reported incorrectly due to noise on the network. The signal to the controller remains for the duration of the collision.

Approximately  $1\mu$ s after the transmission of each packet a signal called the Signal Quality Error (SQE) consisting of typically 10 cycles of 10 MHz is generated. This 10 MHz signal, also called the Heartbeat, ensures the continued functioning of the collision circuitry.

### LINK DETECTOR/GENERATOR

This is a timer circuit that generates a link pulse as shown in the 10BASE-T specification. With a width of 100 ns, the pulse is transmitted every 16 ms on the TXO+ output in the absence of transmit data.

The pulse checks the integrity of the connection to the remote MAU, and the link detection circuit checks for valid pulses from the remote MAU. The link detector will disable the transmit, receive, and collision detection functions if valid link pulses are not received.

To determine that a good twisted-pair link exists, the GDLNK output directly drives an LED; the LED will be on during normal conditions.

### JABBER

Whenever the transmitter is active for greater than 52 ms, the jabber timer monitors the transmitter and disables the transmission. In this case, the transmitter is then disabled for the time that ENDEC module's inter-

nal transmit enable is asserted. This signal has to be deasserted for about 750 ms before the Jabber reenables the transmit outputs.

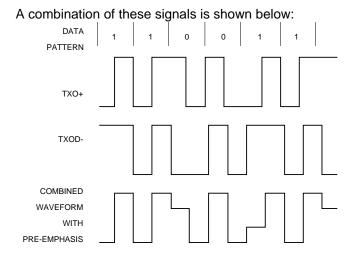

### TRANSMIT DRIVER

The transmitter has four signals, the true and complement Machester-encoded data (TXO $\pm$ ). These signals may be delayed by 50 ns (TXOD $\pm$ ).

These four signals are combined, TXO+ with TXODand TXO- with TXOD+. Known as digital pre-emphasis, this process is required to compensate for the twisted-pair cable which acts like a low-pass filter and can greatly weaken the 10 MHz (50 ns) pulses of the Manchester-encoded waveform than the 5 MHz (100 ns) pulses.

### STATUS INFORMATION

This information is shown at the ENC on the CRS/RX, TXE/TX, COL and POL outputs as decribed in the pin description table. These outputs can drive status LEDs by means of an appropriate driver circuit.

Normally low, the POL output will be driven high when seven consecutive link pulses or three consecutive link pulses having reversed polarity are detected. A wiring error at either end of the TPI cable can cause polarity reversal. Upon detection of this reversal the condition is latched and POL is asserted. Correcting this error is the TP1 and will also decode received data correctly, thus getting rid of the need to check the wiring error.

## MANCHESTER ENCODER AND DIFFERENTIAL DRIVER

On the transformer's secondary, the differential transmit pair drives up to 50 meters of twisted-pair AUI cable. These outputs are source followers requiring two  $270\Omega$  pulldown resistors to ground.

The MX98902 enables both half-step and full-step to be compatible with Ethernet and IEEE 802.3. Transmit+ is positive as regards Transmit- with the SEL pin low (for Ethernet 1). With SEL high (for IEEE 802.3), Transmit+ and Transmit- are equal when idle, thus providing zero differential voltage to operate with transformer-coupled loads.

### MANCHESTER DECODER

This decoder is composed of a differential receiver and a PLL to separate a Manchester-decoded data stream into internal clocks signals and data. When using the standard  $78\Omega$  transceiver drop cable, see that the differential input must be externally terminated with two  $39\Omega$  resistors connected in series. These resistors are optional in Thin Ethernet applications. A squelch circuit at the input rejects signals with levels less than - 175 mV to prevent noise from triggering the decoder. And signals negative than -300 mV are decoded; data becomes valid within 5 bit times. The MX98902 may be able to take bit jitter up to 18 ns in the data that is received.

## **COLLISION TRANSLATOR**

If the Ethernet transceiver, when in AUI mode, detects a collision, it generates a 10 MHz signal to the differential collision inputs (CD $\pm$ ) of the MX98902. When these inputs are active, the MX98902 uses this signal to cancel its current transmission and reschedule another one.

The collision differential inputs are ended in the same way as the differential receive inputs. The squelch circuitry is also similar, rejecting pulses with levels less than -175 mV.

### **RECEIVE DESERIALIZER**

The receive deserializer starts to work when the input signal Carrier Sense is asserted. It allows incoming bits to be shifted into the shift register by the receive clock provided by the SNC (Serial Network Converter). The serial receive data is also routed to the CRC generator/ checker to detect CRC code. The receive deserializer includes a synch detector that detects the SFD (Start of Frame Delimiter) to establish where byte boundaries within the serial bit stream are located, i.e., when a 1,1 bit sequence is detected, it begins to collect data. After every eight receive clocks, the byte-wide data is transferred to the 16-byte FIFO (two 8-byte FIFOs) alternatively and the receive byte count is incremented. The first six bytes after the SFD are checked for valid comparison by the Address Recognition Logic. If the address recognition Logic does not recognize the packet, the FIFO is cleared.

### ADDRESS RECOGNITION LOGIC

The address recognition logic compares the destination address field (first 6 bytes of the received packet) with the physical address registers stored in the address register array, one byte at a time, by the 8th receive clock. If any one of the six bytes does not match the preprogrammed physical address, the protocol PLA rejects the packet. This means that the packet does not belong to the node. All multicast destination addresses are filtered using a hashing technique by latching the 6 most significant bits of the CRC generator. If the multicast address indexes a bit that has been set in the filter bit array of the multicast address register array, the packet is accepted. Otherwise, it is rejected by the Protocol PLA. Each destination address is also checked for all 1's which is the reserved broadcast address.

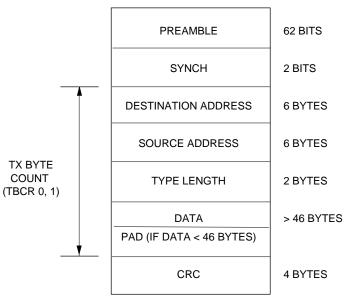

#### PACKET TRANSMISSION

A complete transmit packet consists of Preamble, Synch, Data, and CRC fields. The data field is a contiguous assembled packet of Destination Address. Source Address, Length Field, and Data with the format shown below. During transmit, Page Start Address Register (TPSR) and the Transmit Byte Count Registers (TBCR0,1), control the DMA transfer. As a transmit command is issued to ENC, the packet of data in buffer memory pointed 0 by these registers will be moved into the FIFO. The ENC will generate and append the preamble, synch and CRC fields. In addition, if transmitting data is smaller than 46 bytes, the packet must be padded to a minimum size of 64 bytes. The programmer is responsible for adding and stripping pad bytes.

#### **GENERAL TRANSMIT PACKET FORMAT**

#### CONDITIONS REQUIRED TO BEGIN TRANSMISSION

To initiate transmission of a packet, the TPSR (Transmit Page Start Register) and TBCR0, TBCR1 (Transmit Byte Count Registers) must be initialized and the TXP bit in the Command Register must be set. The ENC will start to prefetch transmit data from memory, if no neception is currently receiving. Three conditions must be met before transmission:

- 1. The Interframe Gap Timer has timed out the first  $6.4 \mu s$  of the Interframe Gap.

- 2. At least one byte has entered the FIFO, which means that burst transfer has begun.

- 3. If collision occurs in the ENC, the backoff timer must expire before retransmit.

If carrier sense is asserted before a byte has been loaded into the FIFO, the ENC will become a receiver.

### **COLLISION RECOVERY**

If transmission has collided with another station, the buffer management logic, which monitors the transmit circuitry will reset the FIFO and restore the Transmit DMA pointers for retransmission of the packet. When collision is detected, the COL bit in TSR will be set and the NCR (Number of Collisions Register) will be incremented. If each of the 15 retransmissions results in a collision, the transmission will be terminated and the ABT bit in the TSR will be set. If excessive collisions (i.e., 16 consecutive collisions) are encountered, NCR reads as zeros and transmission is aborted.

### TRANSMIT PACKET ASSEMBLY FORMAT

The following diagrams show the format for assembling packets before they are transmitted for different byteordering schemes. The various formats are selected in the Data Configuration Register.

DA = Destination Address SA = Source Address

T/L = Type/Length Field

| BIT | D15 D8 | 3 D7  | D0 |

|-----|--------|-------|----|

|     | DA1    | DA0   |    |

|     | DA3    | DA2   |    |

|     | DA5    | DA4   |    |

|     | SA1    | SAO   |    |

|     | SA3    | SA2   |    |

|     | SA5    | SA6   |    |

|     | T/T1   | T/L0  |    |

|     | DATA1  | DATAO |    |

BOS = 0, WTS - 1 in Data Configuration Register. This format is used with Series 32000, 808X-type processors.

| BIT D | D15 D8 | D7 D0 |

|-------|--------|-------|

|       | DA0    | DA1   |

|       | DA2    | DA3   |

|       | DA4    | DA5   |

|       | SA0    | SA1   |

|       | SA2    | SA3   |

|       | SA4    | SA5   |

|       | T/L0   | T/L1  |

|       | DATA0  | DATA1 |

BOS = 1, WTS = 1 in Data Configuration Register. This format is used with 68000-type processors.

| DA0     |

|---------|

| DA1     |

| <br>DA2 |

| DA3     |

| DA4     |

| DA5     |

| SA0     |

| SA1     |

| <br>SA2 |

| SA3     |

|         |

BOS = 0, WTS= 1 in Data Configuration Register. This format is used with general 8-bit CPUs.

## PHYSICAL ADDRESS REGISTERS (PAR0-PAR5)

The physical address registers are used to compare the destination address of incoming packets for rejecting or accepting packets. It compares physical addresses in

PAR0-PAR5 with incoming data one byte at a time. The bit assignment shown below relates the sequence in PAR0-PAR5 to the bit sequence of the received packet.

|      |      |      |      |      | D7               | D6 D5            | D4 D3                   | D2 D1                   | D0 |

|------|------|------|------|------|------------------|------------------|-------------------------|-------------------------|----|

|      | D7   | D6   | D5   | D4   | PA <b>R</b> 8    | DA <b>072</b> DA | 6 DA <b>9</b> 1DA4      | 1 DA <b>B</b> 0DA2      |    |

| PAR0 | DA7  | DA6  | DA5  | DA4  | DA1 DA0<br>DA3   | DA2              | DA1                     | DA0                     |    |

| PAR1 | DA15 | DA14 | DA13 | DA12 | PABA11           |                  | 14DA0300A1              | 12DA01400A01            | C  |

| PAR2 | DA23 | DA22 | DA21 | DA20 | DA9 DA8<br>DA19  | DA18             | DA17                    | DA16                    |    |

| PAR3 | DA31 | DA30 | DA29 | DA28 | PAB227           | DA233216A        | 22 DAØ14, Ø5A2          | 20 DA <b>18</b> 20 A 18 | 3  |

| PAR4 | DA39 | DA38 | DA37 | DA36 | DA17DA10<br>DA35 | 6<br>DA34        | DA33                    | DA32                    |    |

| PAR5 | DA47 | DA46 | DA45 | DA44 |                  |                  | 30 D A <b>B A D</b> A 2 | 28 DA Ø 7 DA 26         | 6  |

|      |      |      |      |      | DA25DA2          | 4                |                         |                         |    |

PAR4 DA39DA38DA37DA36DA35DA34 DA33DA32

PAR5 DA47DA46DA45DA44DA43DA42 DA41DA40 SOURCE

| DESTINATION ADDRESS |     |     |     |     |  |      |      |     |  |  |

|---------------------|-----|-----|-----|-----|--|------|------|-----|--|--|

| P/S                 | DA0 | DA1 | DA2 | DA3 |  | DA46 | DA47 | SA0 |  |  |

NOTE: P/S = Preamble, Synch

DA0 = Physical/Multicast Bit

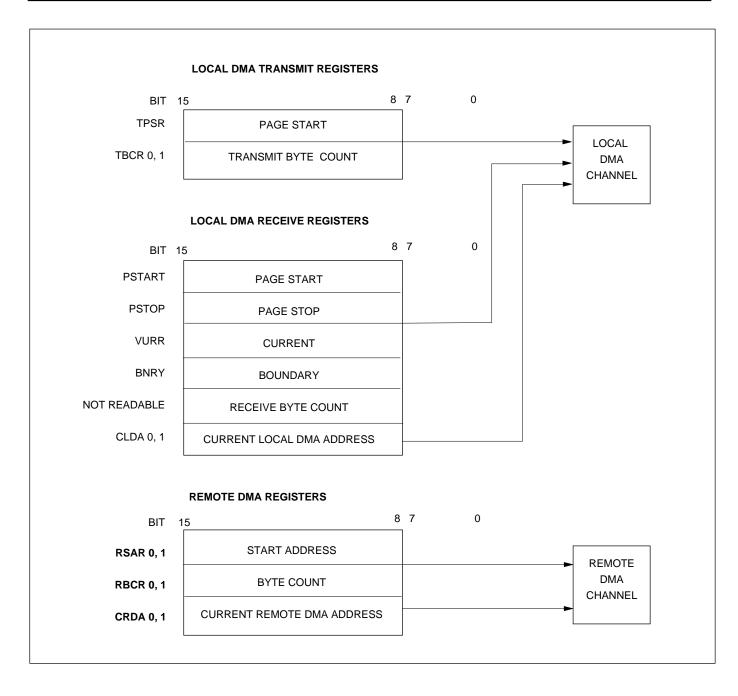

## DIRECT MEMORY ACCESS CONTROL (DMA)

The DMA capabilities of the ENC greatly simplify use of the MX9890 in typical configuration. The local DMA channel transfers data between FIFO, which is inside the ENC, and memory which is outside the ENC. There are two kinds of local DMA type: Local DMA Read and Local DMA Write. Local DMA Read moves data from memory into FIFO on transmission. Should a collision occur (up to 15 times), the packet is retransmitted with no processor intervention. Local DMA Write transfers data from FIFO to memory on reception.

A remote DMA channel is also provided on the ENC to accomplish transfers between a buffer memory and a system memory whenever the I/O map board design is required. The two DMA channels (local DMA and remote DMA) can alternatively be combined to form a single 32bit address with 8- or 16-bit data.

### **DUAL DMA CONFIGURATION**

Network activity is isolated on a local bus, where the ENC's local DMA channel performs burst transfers between the buffer ring and the ENC's FIFO. The remote DMA transfers data between the buffer ring and the host memory by means of a bidirectional I/O port. Meanwhile, remote DMA provides local addressing capability and is used as a slave DMA by the host. Host side addressing must be provided by a host DMA or the CPU. The ENC allows Local and Remote DMA operations to be interleaved because the ENC takes care of the bus arbitration problem itself.

#### SINGLE CHANNEL DMA OPERATION

If desirable, the two DMA channels can be combined to provide a 32-bit DMA address. The upper 16 bits of the 32-bit address provided by the remote DMA channel are static and are used to point to a 64-kbyte (or 32k word) page of memory where packets are to be received or transmitted. The lower 16 bits of the 32-bit address provided by Local DMA channel are dynamic and are used to point to a 64-kbyte (or 32 kword) offset of memory.

## LOOPBACK MODE

Mode1:LoopbackThroughTheNEC Module(LB1=0,L BO=1)

If this loopback is used, the ENC Module's serializer is connected to the deserializer.

Mode 2 : Loopback through the MCC Module (LB1=1, LBO=0)

If this loopback is to be performed through the MCC, the MX98902 provides a control (LBK) that forces the MCC module to loopback all signals.

Mode3 : Loopback to cable (LB1=1, LBO=1) Packets can be transmitted to the cable in loopback mode to check all of the transmit and receive paths and cable itself

**Note** : Collision and Carrrier Sense can be generated by the MCC module and are Masket by the ENC module. It is not possible to go directly between the loopback modes, it is necessary to return to normal (OOH) when changing modes.

## **READING THE LOOPBACK PACKET**

The last 8 bytes of a received packet can be examined by 8 consecutive reads of the FIFO register. The FIFO pointer is incremented after the rising edge of the CPU's read strobe by internally synchronizing and advancing the pointer. This may take up to four bus clock cycles, if the pointer has not been incremented by the time the CPU reads the FIFO registers again, the MX98902 will insery wait states..

## ALIGNMENT OF THE RECEIVED PACKET IN THE FIFO

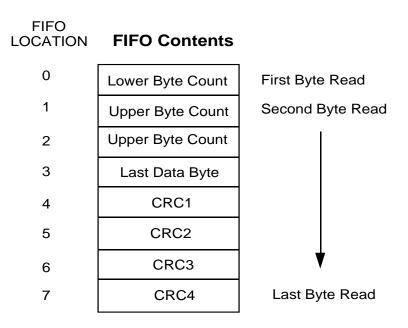

Reception of the packet in the FIFO begins at location zero, after the FIFO pointer reaches the last location in the FIFO, the pointer wraps to the top of the FIFO overwriting the previously received data. This process is continued until the last byte is received. The MX98902 then appends the received byte count in the next two locatioms of the FIFO. The contents of the Upper Byte Count are also copied to the next FIFO location. The number of bytes used in the loopback packet determines the alignment of the FIFO. The alignment for a 8 X N byte packet is shown below.

Figure 5.7.3 FIFO Alignment for 8 X N byte

## **RESTRICTIONS DURING LOOPBACK**

The FIFO is split into two halves, one half is used for transmission and the other for reception. Only 8 bit fields can be fetched from memory so two tests are requires (shown in figure 5.7.4) for 16-bit system to verify integrity of the entire data path. During loopback the maximum latency from the assertion of BREQ to BACK is 2.Ous. Figure A in figure 5.7.4 verify the data path for 680x0 CPU yet figure B verify the data path for 32000/80x86 CPUs.

### LS Byte(AD8-15) MS Byte(AD0-7)

| Destination |

|-------------|

| Sourec      |

| Length      |

| Data        |

| CRC         |

WTS="1" BOS="1" (DCR bits)

Figure A. 680X0 CPU data path verification during loopback

## LS Byte(AD8-15) MS Byte(AD0-7)

| Destination |  |

|-------------|--|

| Sourec      |  |

| Length      |  |

| Data        |  |

| CRC         |  |

WTS="1" BOS="1" (DCR bits)

Figure B. 32000/80x86 CPU data path verification during loopback

### Figure 5.7.4 Data path verification during

## EXAMPLES

The following examples show what results can be expected from a properly operating MX98902 during loopback. The restrictions and results of each type of loopback are listed for reference. The loopback tests are divided into two sets of test. One to verify the data path, CRC generation and byte count through all three paths. the second set of test uses internal loopback to verify the receiver's CRC checking and address recognition. For all of the tests the DCR was programmed to 40H.

| Path            | TCR | RCR | TSR            | RSR            | ISR            |

|-----------------|-----|-----|----------------|----------------|----------------|

| MX9890 Internal | 02  | 1F  | 53<br>(Note 1) | 02<br>(Note 2) | 02<br>(Note 3) |

**Note 1** : Since carrier sense and collision detect are generated in the MCC module, they are blocked during ENC loopbak. Carrier and CD hertbeat are not seen and the CRS and CDH bits are set.

Note 2 : CRC errors are always indicated by the receiver if CRC is appended by the transmitter.

**Note 3**: Only the PTX bit in the ISR is set, the PRX bit is only set if status is written to memory. In loopback this action does not occur and the PRX bit remains 0 for all loopback modes.

Note 4 : All values are hex.

| Path            | TCR | RCR | TSR            | RSR | ISR |

|-----------------|-----|-----|----------------|-----|-----|

| Loopback to MCC | 04  | 1F  | 43<br>(Note 1) | 02  | 02  |

Note 1 : CDH is set, CRS is not set since it is generated by the external MCC module.

| Path            | TCR | RCR | TSR            | RSR | ISR            |

|-----------------|-----|-----|----------------|-----|----------------|

| Loopback to TPI | 06  | 1F  | 03<br>(Note 1) | 02  | 02<br>(Note 2) |

**Note 1** : CDH should not be set. The TSR however, could also contain 01H,03H,07H and a variety of other Values depending on whether collisions were encountered or the packet was deferred. If collision was encountered during sending preamble, then CRS of TSR may be set depending on whether Receive clock is synchrounous to transmit clock or not.

Note 2 : The ISR will contain 08H if packet is not transmittable.

**Note 3**: During exteral loopback the MX98902 is now exposed to network traffic. It is threefore possible for the contents of both the Receive portion of the FIFO and the RSR to be corrupted by any other packer on the network. Thus in a live network the contents of the FIFO and RSR should not be depended on. The MX98902 will still abide by the standard CSMA/CD protocol in external loopback mode. (i.e., The network will not be disturbed by the loopback packet.)

Note 4 : All values are hex.

CRC and Address Recognition

The next three tests exercise the address recognitioon logic and CRC. There tests should be performed using internal loopback only so that the MX98902 is isolated from interference from the network. These tests also require the capability to generaye CRC in software (i.e., CRC inhibibit by transmitter).

The address recognition logic cannot be directly tested. The CRC and FAE bits in the RSR are only set if the address in the packet matches the address filter (PARO - PAR5). If errors are expected to be set and type are not set, the packet has been rejected on the basis of an address mismatch. The following sequence of packets will test the address recognition logic. The DCR should be set to 40H and the TCR should be set to 03H with a software generated CRC.

|        | Packet Conyents | Results |             |

|--------|-----------------|---------|-------------|

| Test   | Address         | CRC     | RSR         |

| Test A | Matching        | Good    | 01 (Note 1) |

| Test B | Matching        | Bad     | 02 (Note 2) |

| Test C | Non-Matching    | Bad     | 01          |

Note 1 : Status will read 21H if multicast address used

Note 2 : Status will read 22H if multicast address used

**Note 3** : In test A, the RSR is set up. In test B the address is found to match since the CRC is flagged as bad. Test C proves that the address recognition logic can distinguish a bad address and does not notify the RSR of the bad CRC. The receiving CRC is proven to work in test A and test B.

Note 4 : All values are hex.

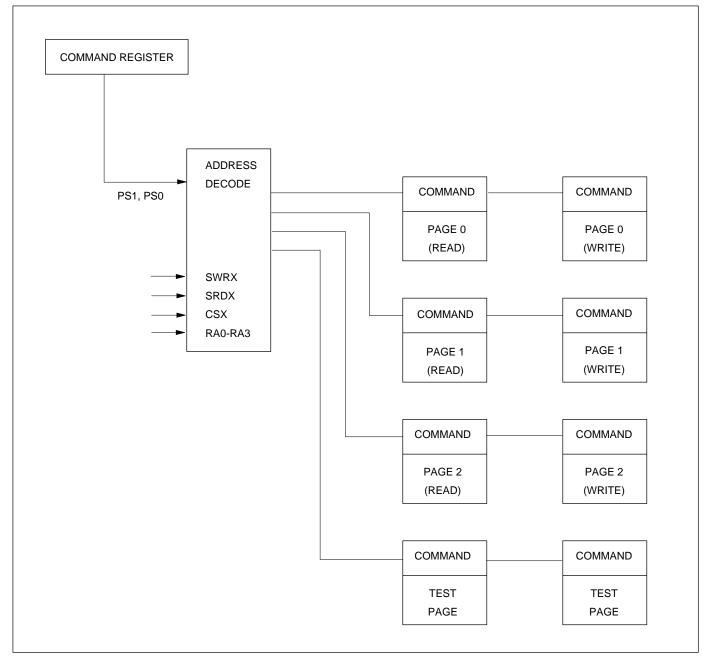

### INTERNAL REGISTERS

All internal registers are mapped into three pages and selected by two bits, PS1 and PS0, of Command Register. Input pins RA0-RA3 are used to address these internal registers which are 8-bit wide and are commonly accessed during ENC register read/write operation. For user's convenience, registers that are commonly accessed during ENC operation are mapped into page 0. Page 1 registers are used primarily for initialization while Page 2 registers are used for diagnostic. Partitioned registers make one write/read cycle possible for accessing those commonly used registers.

### **REGISTER ADDRESS MAPPING**

## **REGISTER DESCRIPTION**

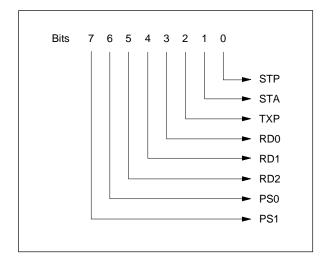

#### A. Command Register (CR) 00H (Read/Write)

The Command Register is used to take the controller on/ off line (STA and STP bits), initiate transmissions (TXP bit), enable or disable Remote DMA operations (RD2, RD1 and RD0 bits), and select register pages (PS1 and PS0). To issue a command, the microprocessor sets the corresponding bit(s). In addition, commands may be overlapped following the guidelines below:

- If a remote DMA operation overlaps a transmission, RD0, RD1 and RD2 must be written with the desired values, and a "0" or "1" may be written to the TXP bit because writing a "0" to TXP has no effect after transmission is activated.

- 2. A remote write DMA may not overlap remote read operation and vice versa. Each operation must either be completed or aborted before starting the other one.

- 3. If a transmit command overlaps with a remote DMA operation, bits RD2, RD1 and RD0 must be maintained for the remote DMA command when setting the TXP bit.

- NOTE: If a remote DMA command is reissued while giving the transmit command, the DMA will complete the process immediately if the remote byte count registers (RBCR1 and RBCR0) have not been reinitialized, i.e., one has to program RBCR0 and/or RBCR1 every time when one needs remote DMA service.

- 4. Bits PS1, PS0, RD2 and STP can be set at any moment.

## REGISTER DESCRIPTION (Continued) A. COMMAND REGISTERS (Continued)

| SYMBOL           | BIT        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| STP              | D0         | <ul> <li>STOP: Software reset command, takes the controller offline; no Packets will be received or transmitted if this bit is set high.</li> <li>Any reception or transmission in progress will enter the reset state after operation is completed. This bit must be cleared and the STA bit must be set high to exit the reset state. The software reset is executed only when the RST bit in the ISR is set to 1. STP powers up high.</li> <li>Note: If the ENC has previously been in start mode and the STP is set, both the STP and STA bits will remain set.</li> </ul> |  |  |  |

| STA              | D1         | <b>START</b> : This bit is used to activate the ENC after either power-up, or when the ENC has been placed in a reset mode by software command or error. STA powers up low.                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| ТХР              | D2         | TRANSMIT PACKET: This bit must be set to initiate transmission of a packet only after<br>the Transmit Byte Count (TBCR1 and TBCR0) and Transmit Page Start register (TPSR)<br>have been programmed. TXP is internally reset either after the transmission is completed<br>or aborted.                                                                                                                                                                                                                                                                                          |  |  |  |

| PD0, PD1,<br>PD2 | D3, D4, D5 | <b>REMOTE DMA COMMAND</b> : These three encoded bits control operation of the Remote<br>DMA channel. RD2 can be set to abort any Remote DMA command in progress. The<br>Remote Byte Count Registers should be cleared by host whenever a Remote DMA has<br>been aborted. The Remote Start Addresses are not restored to the starting address if the<br>Remote DMA is aborted. Hence, for another remote DMA operaton, host should provide<br>a starting address for ENC in order to operate correctly.                                                                         |  |  |  |

|                  |            | RD2RD1RD0000Not Allowed001Remote Read010Remote Write011Send Packet1XXAbort/Complete Remote DMA (Note)                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                  |            | Note: If a remote DMA operation is aborted and the remote byte count has not decremented to zero, PRQ will remain high. A read acknowledge (RACKX) or a write acknowledge (WACKX) will reset PRQ low.                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| PS0, PS1         | D6, D7     | <b>PAGE SELECT</b> : These two encoded bits select which register page is to be accessed with addresses RA0-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                  |            | PS1PS000Register Page 001Register Page 110Register Page 211Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

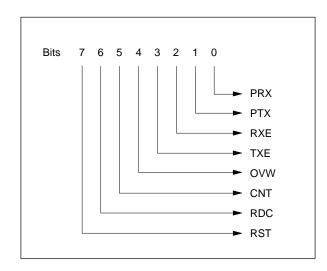

## B. INTERRUPT STATUS REGISTER (ISR) 07H (READ/WRITE)

This register is accessed by the host processor to determine the cause of an interrupt. Any interrupt can be masked in the Interrupt Mask Register (IMR). Individual interrupt bits are cleared by writing a "1" into the corresponding bit of the ISR. The INT signal is active as long as any unmasked signal is set; it will not go low until all unmasked bits in this register have been cleared. The ISR must be cleared after power-up by writing it with all 1's.

| SYMBOL | BIT | DESCRIPTION                                                                                                                                  |

|--------|-----|----------------------------------------------------------------------------------------------------------------------------------------------|

| PRX    | D0  | PACKET RECEIVED: Indicates packet received with no errors.                                                                                   |

| PTX    | D1  | PACKET TRANSMITTED: Indicates packet transmitted with no errors.                                                                             |

| RXE    | D2  | <b>RECEIVE ERROR</b> : Indicates that a packet was received with one or more of the following errors:                                        |

|        |     | <ul> <li>CRC Error</li> <li>Frame Alignment Error</li> <li>FIFO Overrun</li> <li>Missed Packet</li> </ul>                                    |

| TXE    | D3  | <b>TRANSMIT ERROR</b> : Set when packet is transmitted with one or more of the following errors:                                             |

|        |     | <ul><li>Excessive Collisions</li><li>FIFO Underrun</li></ul>                                                                                 |

| OVW    | D4  | <b>OVERWRITE WARNING:</b> Set when receive buffer ring storage resources have been exhausted. (Current Pointer has reached Boundary Pointer) |

## B. INTERRUPT STATUS REGISTER (ISR) 07H (READ/WRITE) (Contiuned)

| SYMBOL | BIT | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                |

|--------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CNT    | D5  | <b>COUNTER OVERFLOW</b> : Set when MSB of one or more of the Network Tally Counters has been set.                                                                                                                                                                                                                                                                          |

| RDC    | D6  | <b>REMOTE DMA COMPLETE:</b> Set when Remote DMA operation has been completed.                                                                                                                                                                                                                                                                                              |

| RST    | D7  | <b>RESET STATUS</b> : Set when ENC enters reset state and cleared when a start command is issued to the CR. This bit is also set when a Receive Buffer Ring overflow occurs and is cleared when one or more packets has been removed from the ring. Writing to this bit has no effect.<br>Note: This bit does not generate any interrupt; it is merely a status indicator. |

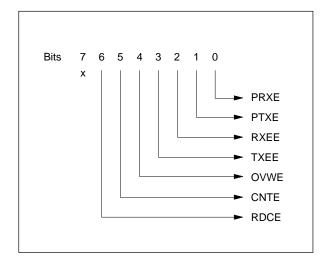

### C. INTERRUPT MASK REGISTER (IMR) 0FH (WRITE)

The Interrupt Mask Register is used to mask interrupts. Each interrupt mask bit corresponds to a bit in the Interrupt Status Register (ISR). If an interrupt mask bit is set, an interrupt will be issued whenever the corresponding bit in the ISR is set. If any bit in the IMR is set low, an interrupt will not occur when the bit in the ISR is set. The IMR powers up all zeros.

# C. INTERRUPT MASK REGISTER (IMR) 0FH (WRITE) (Continued)

| SYMBOL   | BIT | DESCRIPTION                                                                                                                   |

|----------|-----|-------------------------------------------------------------------------------------------------------------------------------|

| PRXE     | D0  | PACKET RECEIVED INTERRUPT ENABLE                                                                                              |

|          |     | 0: Disables Interrupt when packet is received.                                                                                |

|          |     | 1: Enables Interrupt when packet is received.                                                                                 |

| PTXE     | D1  | PACKET TRANSMITTED INTERRUPT ENABLE                                                                                           |

|          |     | 0: Disables Interrupt when packet is transmitted.                                                                             |

|          |     | 1: Enables Interrupt when packet is transmitted.                                                                              |

| RXEE     | D2  | RECEIVE ERROR INTERRUPT ENABLE                                                                                                |

|          |     | 0: Disables Interrupt when packet is received with error.                                                                     |

|          |     | 1: Enables Interrupt when packet is received with error.                                                                      |

| TXEE     | D3  | TRANSMIT ERROR INTERRUPT ENABLE                                                                                               |

|          |     | 0: Disables Interrupt when packet transmission results in error.                                                              |

|          |     | 1: Enables Interrupt when packet transmission results in error.                                                               |

| OVWE     | D4  | OVERWRITE WARNING INTERRUPT ENABLE                                                                                            |

|          |     | <ol> <li>Disables Interrupt when Buffer Management Logic lacks sufficient buffers to store an<br/>incoming packet.</li> </ol> |

|          |     | 1: Enables Interrupt when Buffer Management Logic lacks sufficient buffers to store an                                        |

|          |     | incoming packet.                                                                                                              |

| CNTE     | D5  | COUNTER OVERFLOW INTERRUPT ENABLE                                                                                             |

|          |     | 0: Disables Interrupt when MSB of one or more of the Network Statistics Counters has                                          |

|          |     | been set.<br>1: Enables Interrupt when MSB of one or more of the Network Statistics Counters has                              |

|          |     | been set.                                                                                                                     |

| RDCE     | D6  | DMA COMPLETE INTERRUPT ENABLE                                                                                                 |

|          |     | 0: Disables Interrupt when Remote DMA transfer has been completed.                                                            |

|          |     | 1: Enables Interrupt when Remote DMA transfer has been completed.                                                             |

| RESERVED | D7  | Reserved                                                                                                                      |

### P. NATERRUPFWRASK REGISTER (MRR) OFH (WRITE) (WRITE) (Continued)

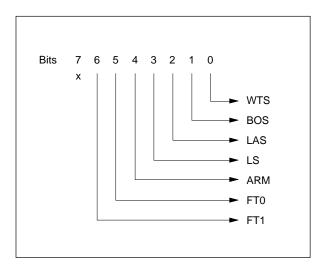

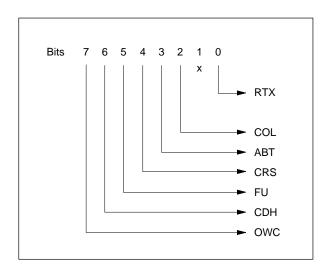

This register is used to program the ENC for 8- or 16-bit SYMBOLE BOD, SPESCIIPATION opback operation, select byte ordering in 16-bit application, and establish FIFO threshold. The DCR must be initialized prior to loading the Remote Byte Count Registers. LAS is set on power-up.